2019年10月7日19:13:37 待提升:分布式计算研究(参考:http://www.elecfans.com/d/782268.html) 以及各种改进实现思路的论文: 基本型FIR实现: 需要具备的应用: 1)乘法器; 2)加法器; 3)延

2019年10月7日19:13:37

待提升:分布式计算研究(参考:http://www.elecfans.com/d/782268.html)

以及各种改进实现思路的论文:

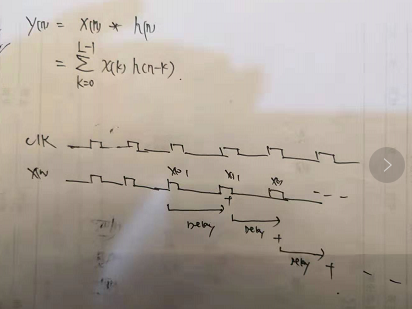

基本型FIR实现:

需要具备的应用:

1)乘法器;

2)加法器;

3)延时器;

以6阶FIR举例——

对应code

`timescale 1ns / 1ps

module fir_6tap(

input Clk,

input signed [15:0] Xin,

output reg signed [23:0] Yout

);

//Internal variables.

wire signed [7:0] H0,H1,H2,H3,H4,H5;

wire signed [23:0] MCM0,MCM1,MCM2,MCM3,MCM4,MCM5,add_out1,add_out2,add_out3,add_out4,add_out5;

wire signed [23:0] Q1,Q2,Q3,Q4,Q5;

//filter coefficient initializations.

//H = [-2 -1 3 4] 8bits

assign H0 = -15;

assign H1 = 19 ;

assign H2 = 123;

assign H3 = 123;

assign H4 = 19;

assign H5 = -15;

//Multiple constant multiplications.

assign MCM5 = H5*Xin;

assign MCM4 = H4*Xin;

assign MCM3 = H3*Xin;

assign MCM2 = H2*Xin;

assign MCM1 = H1*Xin;

assign MCM0 = H0*Xin;

//adders

assign add_out1 = Q1 + MCM4;

assign add_out2 = Q2 + MCM3;

assign add_out3 = Q3 + MCM2;

assign add_out4 = Q4 + MCM1;

assign add_out5 = Q5 + MCM0;

//flipflop instantiations (for introducing a delay).

DFF dff1 (.Clk(Clk),.D(MCM5),.Q(Q1));

DFF dff2 (.Clk(Clk),.D(add_out1),.Q(Q2));

DFF dff3 (.Clk(Clk),.D(add_out2),.Q(Q3));

DFF dff4 (.Clk(Clk),.D(add_out3),.Q(Q4));

DFF dff5 (.Clk(Clk),.D(add_out4),.Q(Q5));

//Assign the last adder output to final output.

[email protected] (posedge Clk)

Yout <= add_out5;

endmodule

对于任意阶:

module fir6Tap(clk, rst, xin, yout);

/******************** PARAMETER ********************/

parameter DATINWIDTH = 16;

parameter COEFWIDTH = 8;

parameter DATOUTWIDTH = COEFWIDTH + DATINWIDTH ;

parameter FIRTAPS = 6;

/******************** INPUT OUTPUT ********************/

input clk;

input rst;

input signed [DATINWIDTH - 1:0] xin;

output reg signed [DATOUTWIDTH - 1:0] yout;

/******************** FIR ********************/

wire signed [COEFWIDTH - 1:0] firCoef [FIRTAPS - 1:0] = {

-8‘d15,

8‘d19,

8‘d123,

8‘d123,

8‘d19,

-8‘d15

};

wire signed [DATOUTWIDTH - 1:0] dataMult [FIRTAPS - 1:0];

reg signed [DATOUTWIDTH - 1:0] dataDelay [FIRTAPS - 2:0];

wire signed [DATOUTWIDTH - 1:0] dataOut [FIRTAPS - 2:0];

genvar ii;

generate

for(ii = 0; ii < FIRTAPS - 1; ii = ii + 1) begin

assign dataMult[ii] = firCoef[ii] * xin;

assign dataOut[ii] = dataDelay[ii] + dataMult[FIRTAPS - 2 - ii];

end

endgenerate

assign dataMult[FIRTAPS - 1] = firCoef[FIRTAPS - 1] * xin;

genvar jj;

generate

for (jj = 1; jj < FIRTAPS - 1; jj = jj + 1)

always @(posedge clk) begin

dataDelay[jj] <= dataOut[jj - 1];

end

endgenerate

always @(posedge clk) begin

dataDelay[0] <= dataMult[FIRTAPS - 1];

end

always @(posedge clk) begin

yout <= dataOut[FIRTAPS - 2];

end

endmodule