CXP定义了一个DEVICE和HOST之间点对点的连接协议。CXP的一个连接包含了一个MASTER物理连接和若干可选的SLAVE连接,每一个连接都定义了一组逻辑通道用于传输图像数据、实时触发、设备控制等。

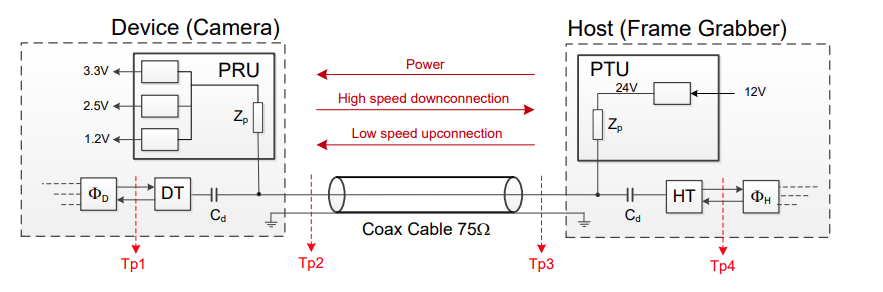

连接类型 upconnection and downconnection1、Power

2、upconnection(分为低速和高速2种,高速需要额外的物理支持);

3、downconnection

upconnection

指HOST到DEVICE的数据传输,CXP协议中对应的20.83Mbps和41.96Mbps指的就是这个连接,协议也支持可选的高速upconnection 连接,和downconnection 工作在相同的bit速率下,这样可以提供更好的触发传输速度、更好的控制性能,不过这个需要额外的一条同轴线缆、收发器的支持,实际上增加了设备的成本和复杂度,目前我接触到的设备都不具备这个功能。

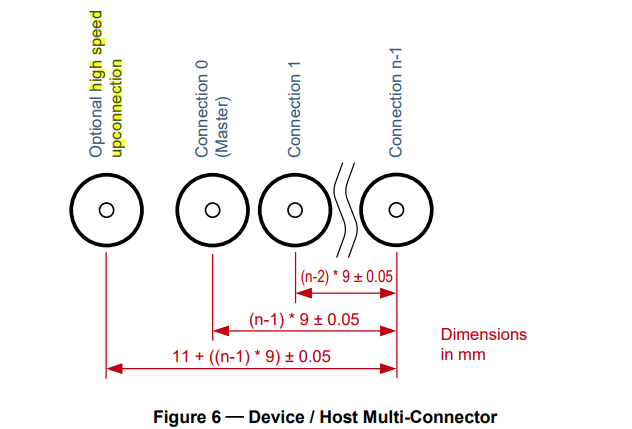

下图可以看到,高速upconnection这个东西需要额外线缆连接的。

指DEVICE到HOST的数据传输,高速数据流,CXP所讲的多少Gbps就是指这个速度,支持从1.25Gbps到12.5Gbps的bit速率

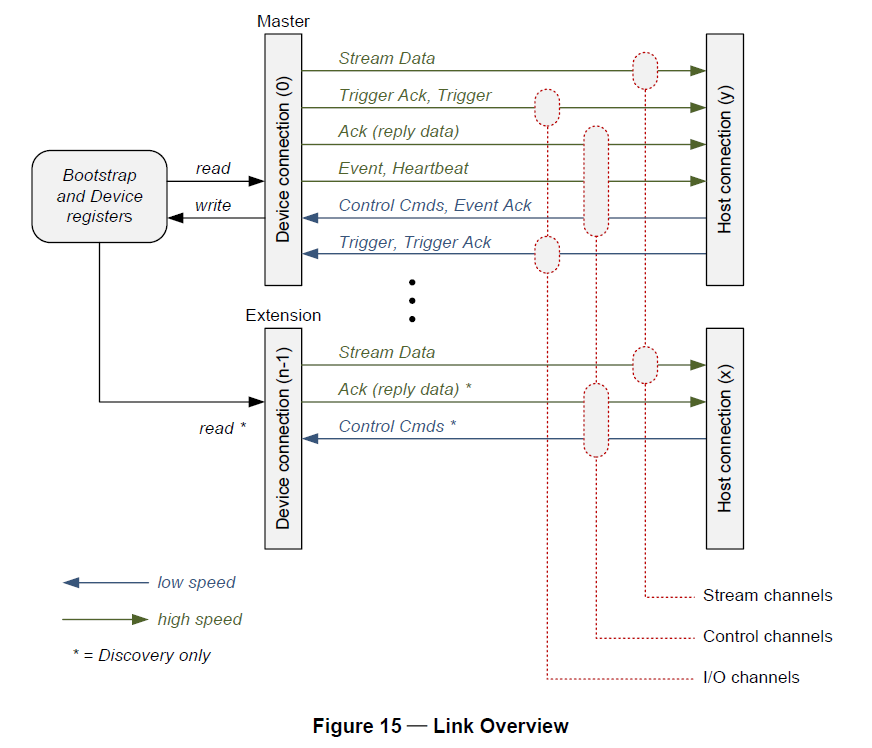

下面这个示意图是没有高速upconnection 连接时对应的数据流示意图,如果设备支持高速upconnection,当设备连接成功后就可以使用高速upconnection 代替低速的数据传输,从而使得寄存器的读写控制更快。

下图做一点说明,Bootstrap register指的是Gencam 编程模型定义的基础寄存器,Device register顾名思义就是Device的寄存器。

图中定义了3组通道:stream channels, IO channels, control channels,这3个通道所包含的传输类型、所在通道也在图中有明确的标注,后续会对这3个通道的传输层具体格式进行解释

FPGA, PCIe,ZYNQ, C#,C++ 2897551649@qq.com