RCC 即Reset and Clock Control ,意思是复位和时钟控制器,它负责单片机的复位以及时钟的配置。

1.复位

STM32F10xxx支持三种复位形式,分别为系统复位、电源复位和备份区域复位。

(1)系统复位 当发生以下任一事件时,产生一个系统复位:

1. NRST引脚上的低电平(外部复位)

2. 窗口看门狗计数终止(WWDG复位)

3. 独立看门狗计数终止(IWDG复位)

4. 软件复位(SW复位)

5. 低功耗管理复位

除了时钟控制器的RCC_CSR寄存器中的复位标志位和备份区域中的寄存器以外,系统

复位将复位所有寄存器至它们的复位状态。

当以下事件中之一发生时,产生电源复位:

1. 上电/掉电复位(POR/PDR复位)

2. 从待机模式中返回

电源复位将复位除了备份区域外的所有寄存器。

(3)备份域复位 当以下事件中之一发生时,产生备份区域复位。

1. 软件复位,备份区域复位可由设置备份域控制寄存器 (RCC_BDCR)中的BDRST位产生。

2. 在VDD和VBAT两者掉电的前提下, VDD或VBAT上电将引发备份区域复位。

备份区域拥有两个专门的复位,它们只影响备份区域。

2.时钟时钟系统为硬件系统的各个模块提供时钟信号,就像人的脉搏心跳一样不可或缺,而STM32的结构较为复杂,不同的硬件可能对时钟信号有不同的要求,因此在系统中设置多个振荡器,分别提供时钟信号,实际中经常从一个主振荡器开始,经过多次的倍频、分频、锁相环等电路,生成每个模块的时钟信号。

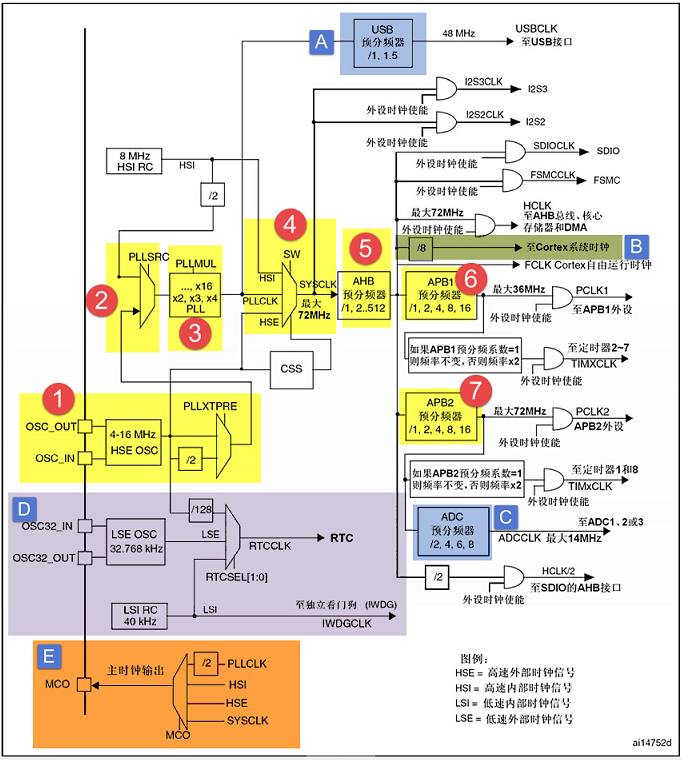

下图为单片机的时钟树,它描述了整个系统从振荡器到各个模块的时钟信号通路。

这个图初看可能会觉得比较复杂,但只要抓住核心,也就容易了,其核心就是图中标号4的部分,SYSCLK系统时钟。

我们可以把时钟树以SYSCLK为界限分为左右两部分,左边是驱动SYSCLK所需的振荡器输入、分频、锁相环倍频等过程,而右边是SYSCLK提供给总线以及各个外设的时钟信号通路。

左边:

有三种不同的时钟源可被用来驱动系统时钟(SYSCLK):HSI振荡器时钟、HSE振荡器时钟 和 PLL时钟。

PLL时钟是Phase Lock Loop时钟即“锁相环时钟”的简称,它利用外部输入的参考信号控制环路内部振荡信号的频率和相位,故可以实现外部控制倍频的效果。

PLL锁相环时钟被三种时钟源其中之一驱动,分别是HSI/2 、HSE 和 HSE/2。

右边:

由图中5、6、7三个预分频器控制HCLK、PCLK1和PCLK2的时钟频率,其中HCLK1最大只能达到36M,而HCLK2可以达到72M。

由HLK、PCLK1、PCLK2这三个总线时钟,经过分频和倍频产生其他外设需要的时钟频率。

其他:

LSE、LSI用来产生RTC实时时钟 和 IWDG独立看门狗时钟。

由PLLCLK/2、HSI、HSE、SYSCLK这四个其中之一,可以向单片机外部输出MCO时钟信号,对应单片机PA8引脚。

二、探究系统的初始化时钟配置函数

在启动文件“startup_stm32f10x_hd.s”中,有这样一段汇编代码,当系统复位时执行,效果是初始化系统的时钟,并运行__main这段代码,最终执行我们写的main函数。

; Reset handler

Reset_Handler PROC

EXPORT Reset_Handler [WEAK]

IMPORT __main

IMPORT SystemInit

LDR R0, =SystemInit

BLX R0

LDR R0, =__main

BX R0

ENDP说一个题外话:

__main和main是完全两个不同的函数,并且你无法找到__main代码,因为这个是编译器自动创建的。

查看MDK的文档,会发现有这么一句说明:It is automatically created by the linker when it sees a definition of main(),意思是当编译器发现定义了main函数,那么就会自动创建__main。

我们这里关注SystemInit这个函数,它初始化了系统的时钟配置,对函数go to definition后发现该函数定义在“system_stm32f10x.c”中,其函数内容如下。

启动文件中调用的的系统初始化函数

/**

* @brief Setup the microcontroller system

* Initialize the Embedded Flash Interface, the PLL and update the

* SystemCoreClock variable.

* @note This function should be used only after reset.

* @param None

* @retval None

*/

void SystemInit (void)

{

/* Reset the RCC clock configuration to the default reset state(for debug purpose) */

/* Set HSION bit */

RCC->CR |= (uint32_t)0x00000001;

/* Reset SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO bits */

#ifndef STM32F10X_CL

RCC->CFGR &= (uint32_t)0xF8FF0000;

#else

RCC->CFGR &= (uint32_t)0xF0FF0000;

#endif /* STM32F10X_CL */

/* Reset HSEON, CSSON and PLLON bits */

RCC->CR &= (uint32_t)0xFEF6FFFF;

/* Reset HSEBYP bit */

RCC->CR &= (uint32_t)0xFFFBFFFF;

/* Reset PLLSRC, PLLXTPRE, PLLMUL and USBPRE/OTGFSPRE bits */

RCC->CFGR &= (uint32_t)0xFF80FFFF;

#ifdef STM32F10X_CL

/* Reset PLL2ON and PLL3ON bits */

RCC->CR &= (uint32_t)0xEBFFFFFF;

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x00FF0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#else

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

#endif /* STM32F10X_CL */

#if defined (STM32F10X_HD) || (defined STM32F10X_XL) || (defined STM32F10X_HD_VL)

#ifdef DATA_IN_ExtSRAM

SystemInit_ExtMemCtl();

#endif /* DATA_IN_ExtSRAM */

#endif

/* Configure the System clock frequency, HCLK, PCLK2 and PCLK1 prescalers */

/* Configure the Flash Latency cycles and enable prefetch buffer */

SetSysClock();

#ifdef VECT_TAB_SRAM

SCB->VTOR = SRAM_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal SRAM. */

#else

SCB->VTOR = FLASH_BASE | VECT_TAB_OFFSET; /* Vector Table Relocation in Internal FLASH. */

#endif

}

函数内部基本是对RCC寄存器的配置,前面大部分语句都是把RCC寄存器初始化成默认的复位状态,最后又调用了SetSysClock()这个函数,函数内部内容如下。

SetSysClock()函数

/**

* @brief Configures the System clock frequency, HCLK, PCLK2 and PCLK1 prescalers.

* @param None

* @retval None

*/

static void SetSysClock(void)

{

#ifdef SYSCLK_FREQ_HSE

SetSysClockToHSE();

#elif defined SYSCLK_FREQ_24MHz

SetSysClockTo24();

#elif defined SYSCLK_FREQ_36MHz

SetSysClockTo36();

#elif defined SYSCLK_FREQ_48MHz

SetSysClockTo48();

#elif defined SYSCLK_FREQ_56MHz

SetSysClockTo56();

#elif defined SYSCLK_FREQ_72MHz

SetSysClockTo72();

#endif

函数内部判断是否定义了SYSCLK_FREQ_72MHz,如果有定义过,则执行SetSysClockTo72();这个函数,而根据“system_stm32f10x.c”这一源文件的代码,对stm32f10x的HD型设备,其默认定义了SYSCLK_FREQ_72MHz。

HD型设备默认定义

#if defined (STM32F10X_LD_VL) || (defined STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)

/* #define SYSCLK_FREQ_HSE HSE_VALUE */

#define SYSCLK_FREQ_24MHz 24000000

#else

/* #define SYSCLK_FREQ_HSE HSE_VALUE */

/* #define SYSCLK_FREQ_24MHz 24000000 */

/* #define SYSCLK_FREQ_36MHz 36000000 */

/* #define SYSCLK_FREQ_48MHz 48000000 */

/* #define SYSCLK_FREQ_56MHz 56000000 */

#define SYSCLK_FREQ_72MHz 72000000

#endif

由于默认定义,会执行SetSysClockTo72()函数,函数内部如下。

SetSysClockTo72()函数

#elif defined SYSCLK_FREQ_72MHz

/**

* @brief Sets System clock frequency to 72MHz and configure HCLK, PCLK2

* and PCLK1 prescalers.

* @note This function should be used only after reset.

* @param None

* @retval None

*/

static void SetSysClockTo72(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

/* Enable HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/* Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

/* Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/* Flash 2 wait state */

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

#ifdef STM32F10X_CL

/* Configure PLLs ------------------------------------------------------*/

/* PLL2 configuration: PLL2CLK = (HSE / 5) * 8 = 40 MHz */

/* PREDIV1 configuration: PREDIV1CLK = PLL2 / 5 = 8 MHz */

RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |

RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);

RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |

RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV5);

/* Enable PLL2 */

RCC->CR |= RCC_CR_PLL2ON;

/* Wait till PLL2 is ready */

while((RCC->CR & RCC_CR_PLL2RDY) == 0)

{

}

/* PLL configuration: PLLCLK = PREDIV1 * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL9);

#else

/* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

#endif /* STM32F10X_CL */

/* Enable PLL */

RCC->CR |= RCC_CR_PLLON;

/* Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{ /* If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

}

}

#endif函数总体流程为:

- 使能HSE

- 等待HSE使能完毕

- 使能预取指

- 设置FLASH等待2个周期

- 配置HCLK

- 配置PCLK2

- 配置PCLK1

- 配置PLL锁相环时钟,包含两个参数,分别是锁相环的时钟源和倍频系数

- 使能PLL锁相环

- 等待PLL锁相环稳定

- 配置PLL锁相环作为SYSCLK系统时钟

- 等待PLL锁相环成功配置为SYSCLK源

三、自己写HSE配置系统时钟函数

如果不使用系统自带的RCC初始化函数,我们自己也可以根据库函数仿照系统自带的流程写出一个配置函数,所需要的库函数,在"stm32f10x_rcc.c"中有定义,在"stm32f10x_rcc.h"最下方有声明,可以很方便地找到。

仿照系统自带的配置流程,依据"stm32f10x_rcc.c"库函数,写出的HSE配置系统时钟函数如下。

HSE配置系统时钟函数

void HSE_SetSysClk(uint32_t RCC_PLLMul_x)

{

ErrorStatus HSEStatus;

//把RCC寄存器复位成复位值

RCC_DeInit();

//使能HSE

RCC_HSEConfig(RCC_HSE_ON);

//等待HSE准备完毕

HSEStatus = RCC_WaitForHSEStartUp();

if(HSEStatus == SUCCESS)

{

//使能预取指缓冲

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

//设置FLASH等待2个周期

FLASH_SetLatency(FLASH_Latency_2);

//设置HCLK,即AHB的时钟频率为不分频

RCC_HCLKConfig(RCC_SYSCLK_Div1);

//设置PCLK2时钟频率为不分频

RCC_PCLK2Config(RCC_HCLK_Div1);

//设置PCLK1时钟频率为2分频

RCC_PCLK1Config(RCC_HCLK_Div2);

//设置PLL锁相环时钟为HSE*x, x为函数的入口参数。

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_x);

//使能PLL锁相环

RCC_PLLCmd(ENABLE);

//等待PLL稳定

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET) ;

//配置PLL作为系统时钟

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

//等待PLL成功设置为SysClk源

while(RCC_GetSYSCLKSource() != 0x08) ;

}

else

{

/* If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

}

}