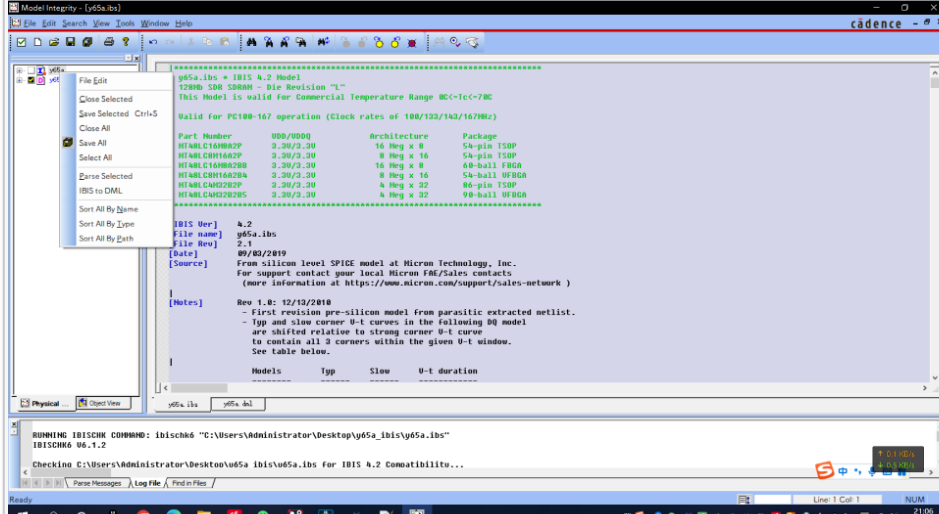

Allegro PCB SI在仿真时需要将仿真模型都转变成DML模型格式。这一操作通过cadence软件组内的Model Integrity软件完成。首先在对应控制器芯片和DDR芯片,flash芯片(需要仿真的驱动和被驱动端)官网找到对应的ibis模型。以本项目的控制器DSP6713,SST39VF800A,MT48LC2M32B2B5-6为例,在各自官网找到ibis模型文件,下载之后通过Model Integrity转换成dml文件。官网下载的文件不一定能百分之百转换成功,过程中可能会报error,根据对应提示修改或删除对应报错行的代码。

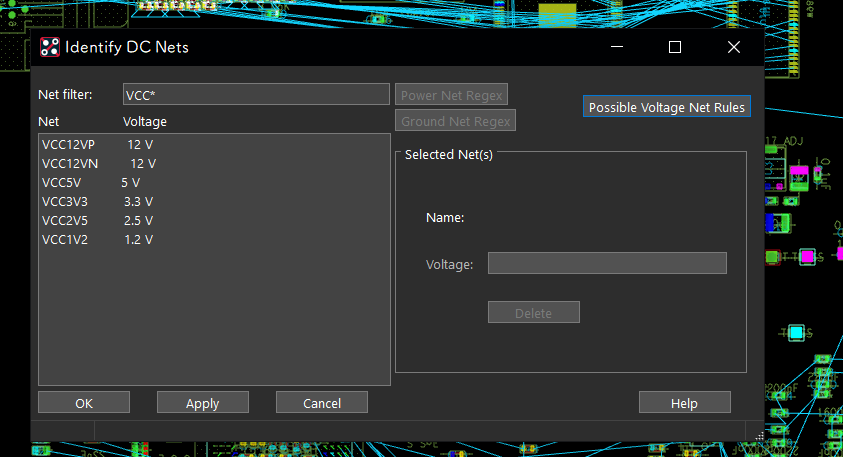

然后将dml文件复制到项目文件夹内,首先进行PCB的叠层设置控制阻抗,然后再identity dc nets中对电源和地赋予电压值。

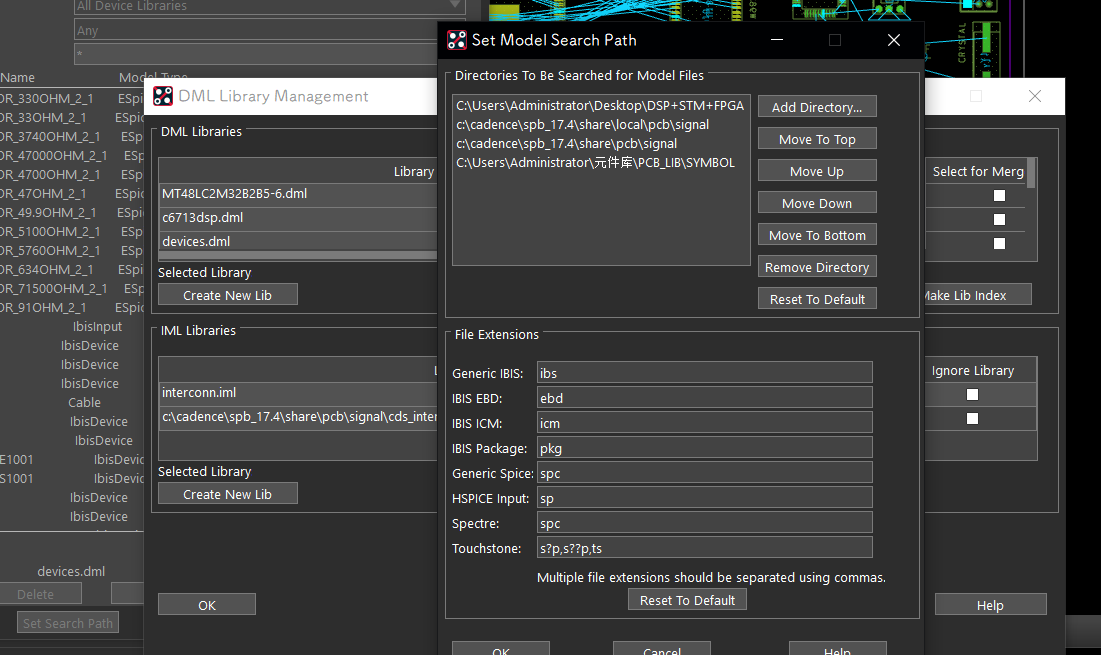

接着在Analyse-Model Browser-library Mgmt-set search path导入对应dml文件。

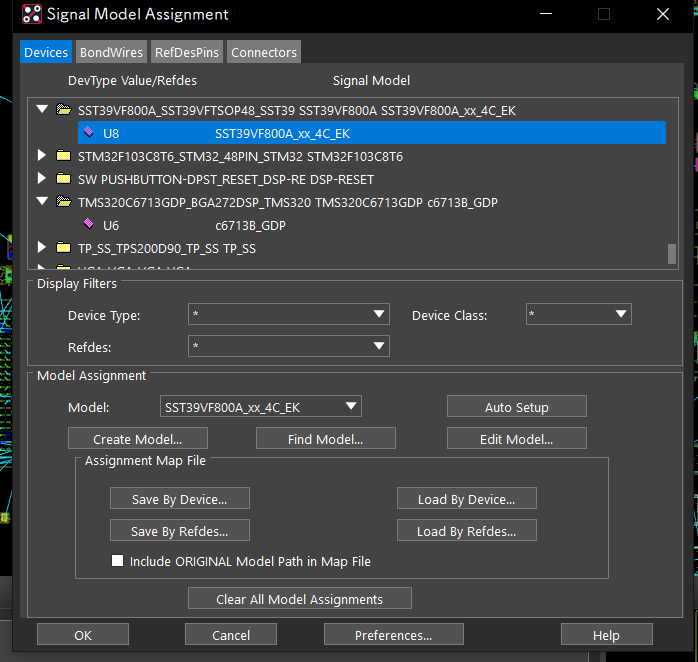

接着打开Analyse-Model Assignment,无视出现的warning。

选择对应的元器件,点击Find Model选择对应的模型assign。由于DSP控制器地址线数据线进行了端接,对于分立器件,如电阻电容,排阻,也需要赋予对应的model,和仿真的网络形成xnet。然后打开cm约束管理器,对数据线和地址线进行分组。添加到net group。然后右击DSP_DATA,选择SigXplorer提取拓扑。

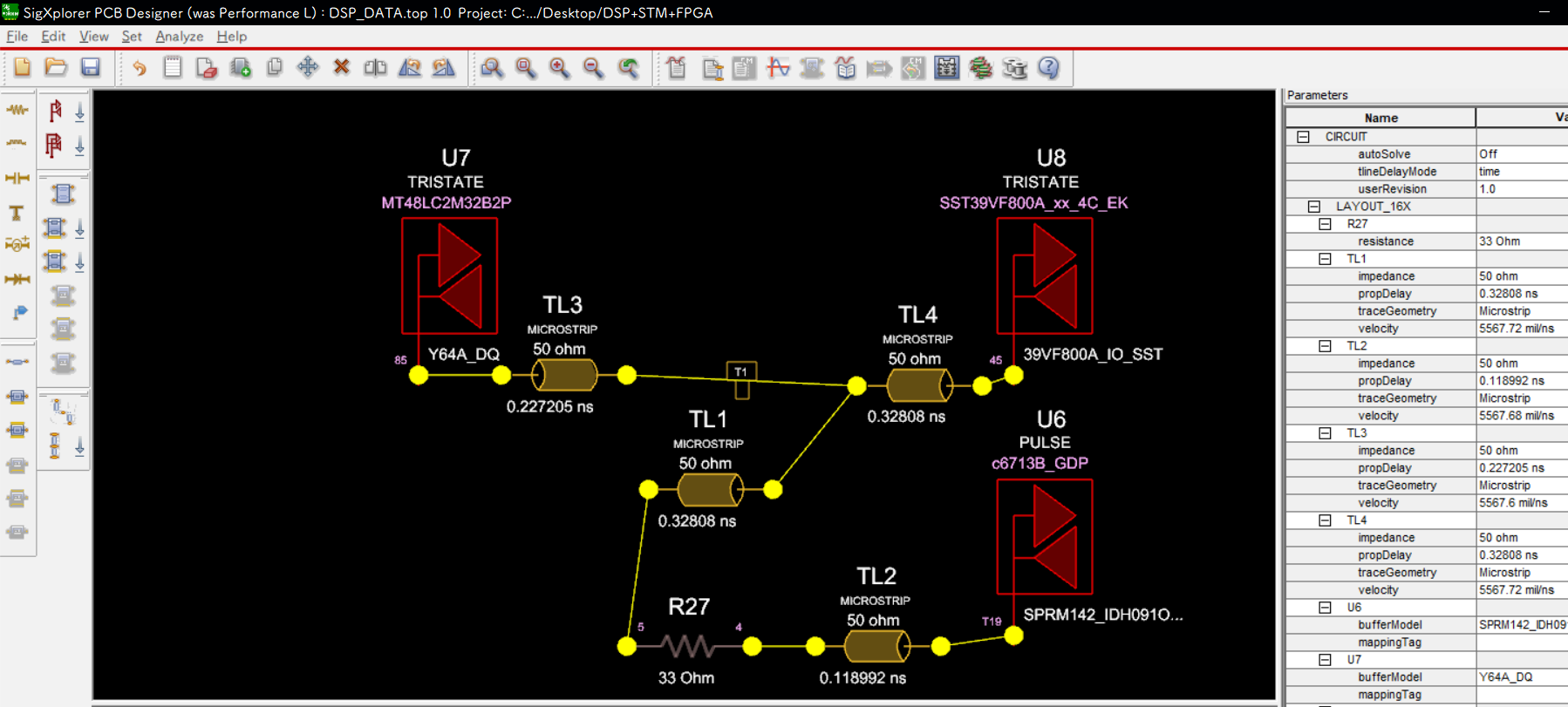

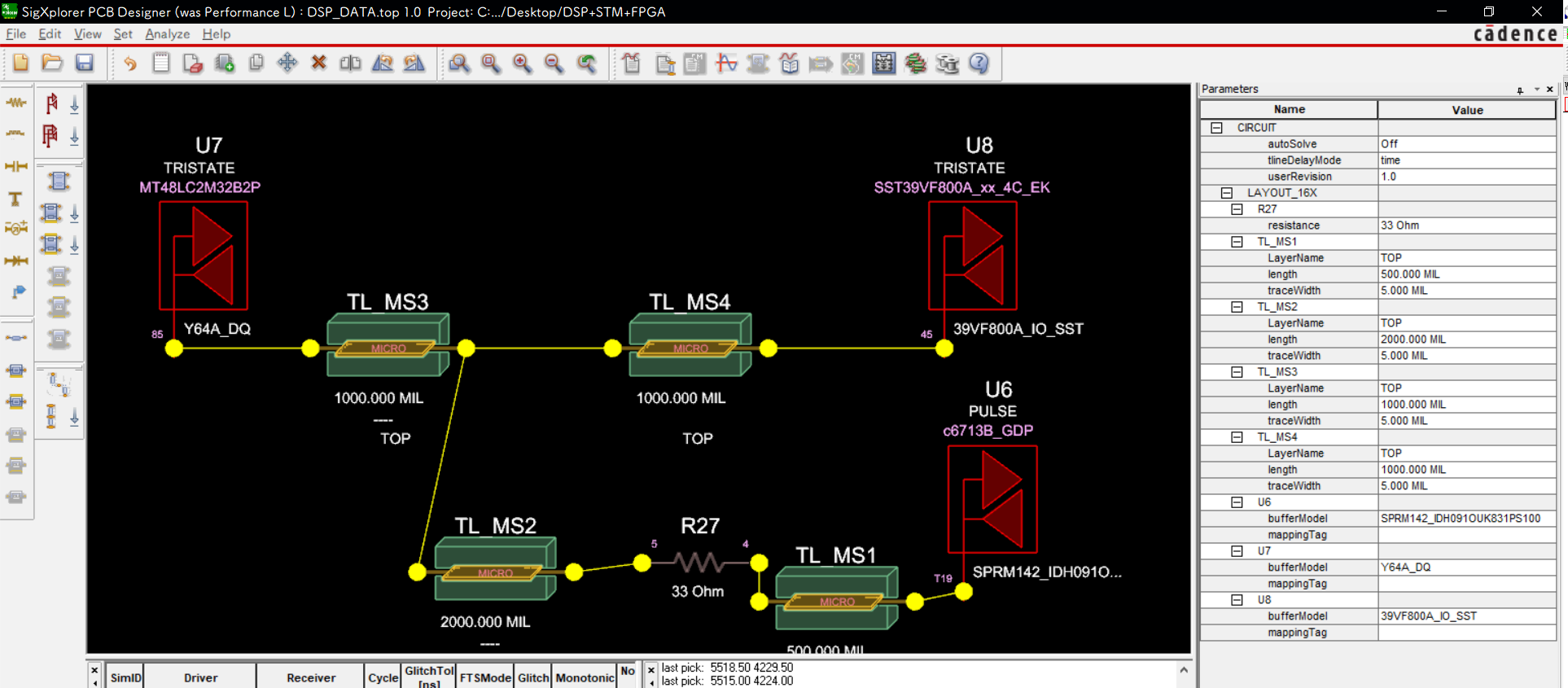

默认拓扑的微带线是理想的,实际要使用有损互联的微带线,数据信号同时连接SDRAM U7和flashU8,在中间建立T型连接点。

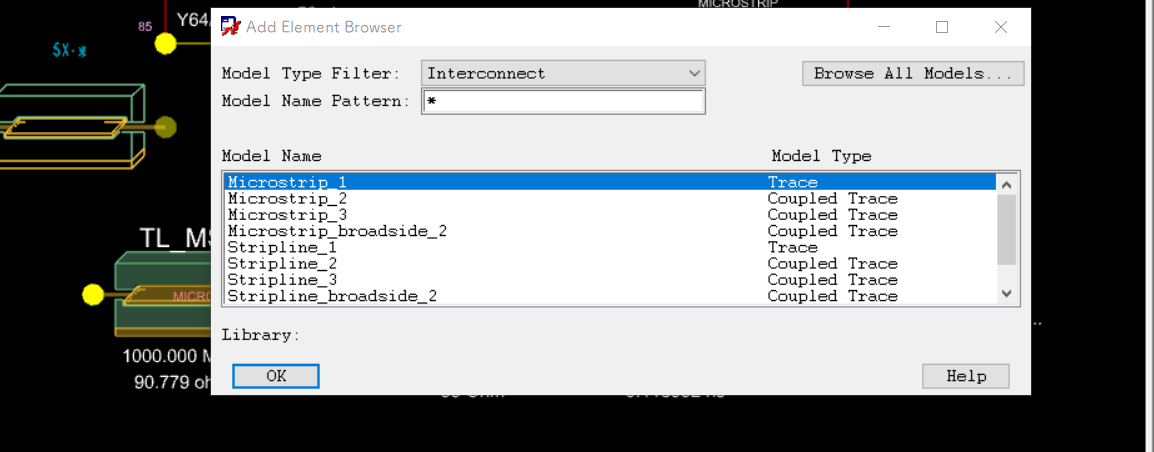

点击add-edit part,加入有损传输线模型。

LayerName选择TOP,前面已进行对叠层的设置。

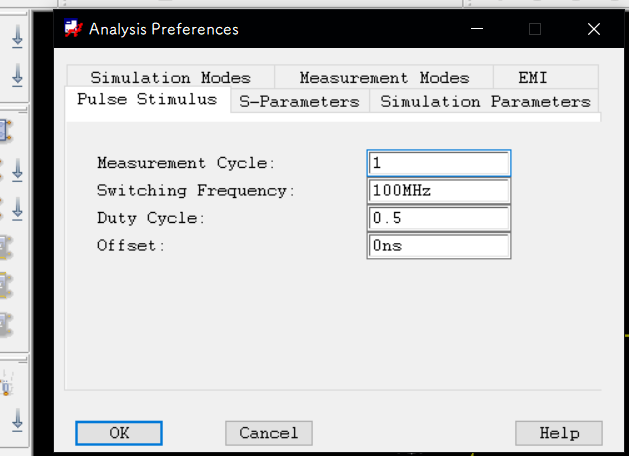

状态栏选择preference,在100MHZ的条件下 ,点击

,点击

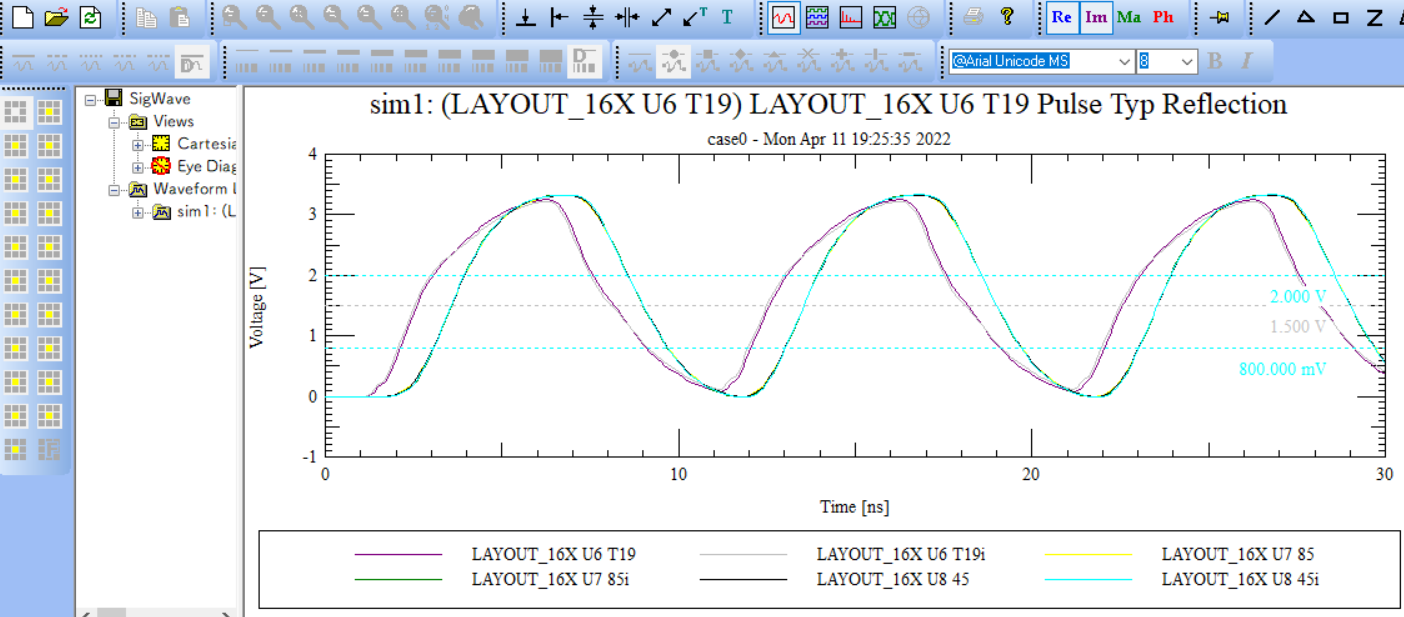

取得的波形如下:

注意:我在仿真过程中发现最新的cadence17.4在进行最后一步仿真时报错,改用17.2版本之后错误消失。不清楚是个例还是普遍情况。

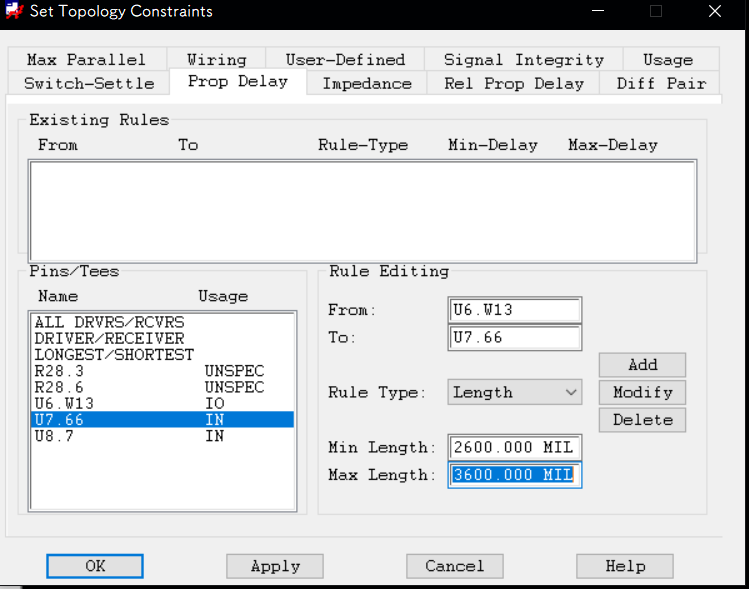

然后对拓扑进行约束,在setup-constraint中选择Prop Dealy,From为U6,To为U7,代表从DSP6713到SDRAM的长度控制,长度经过如上仿真得到。

对于另一组信号线DSP_ADDR也用相同的方法设置,长度为2000mil到3000mil。

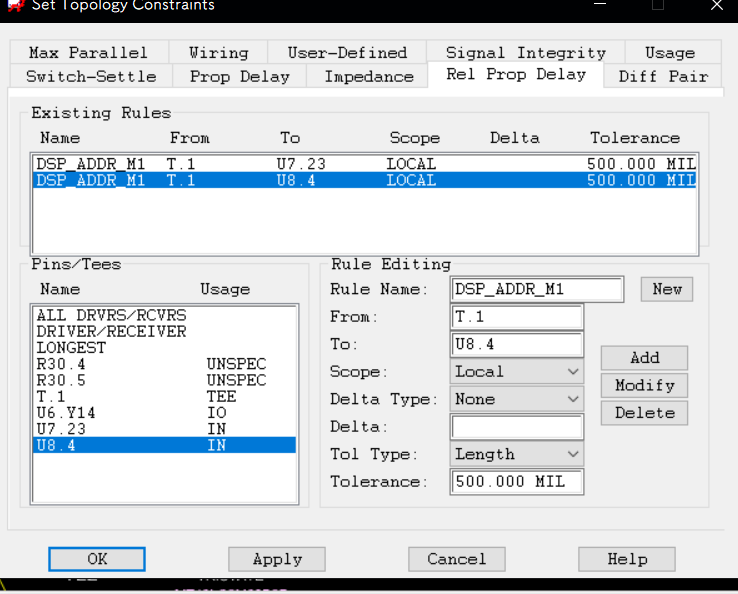

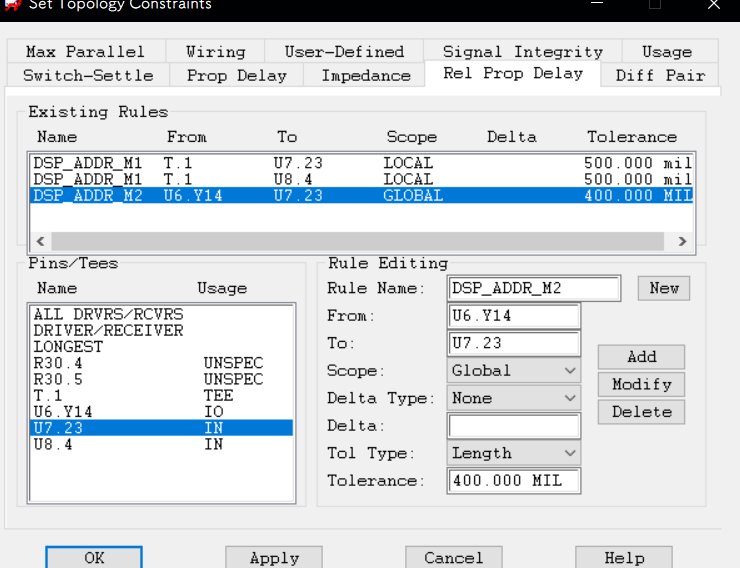

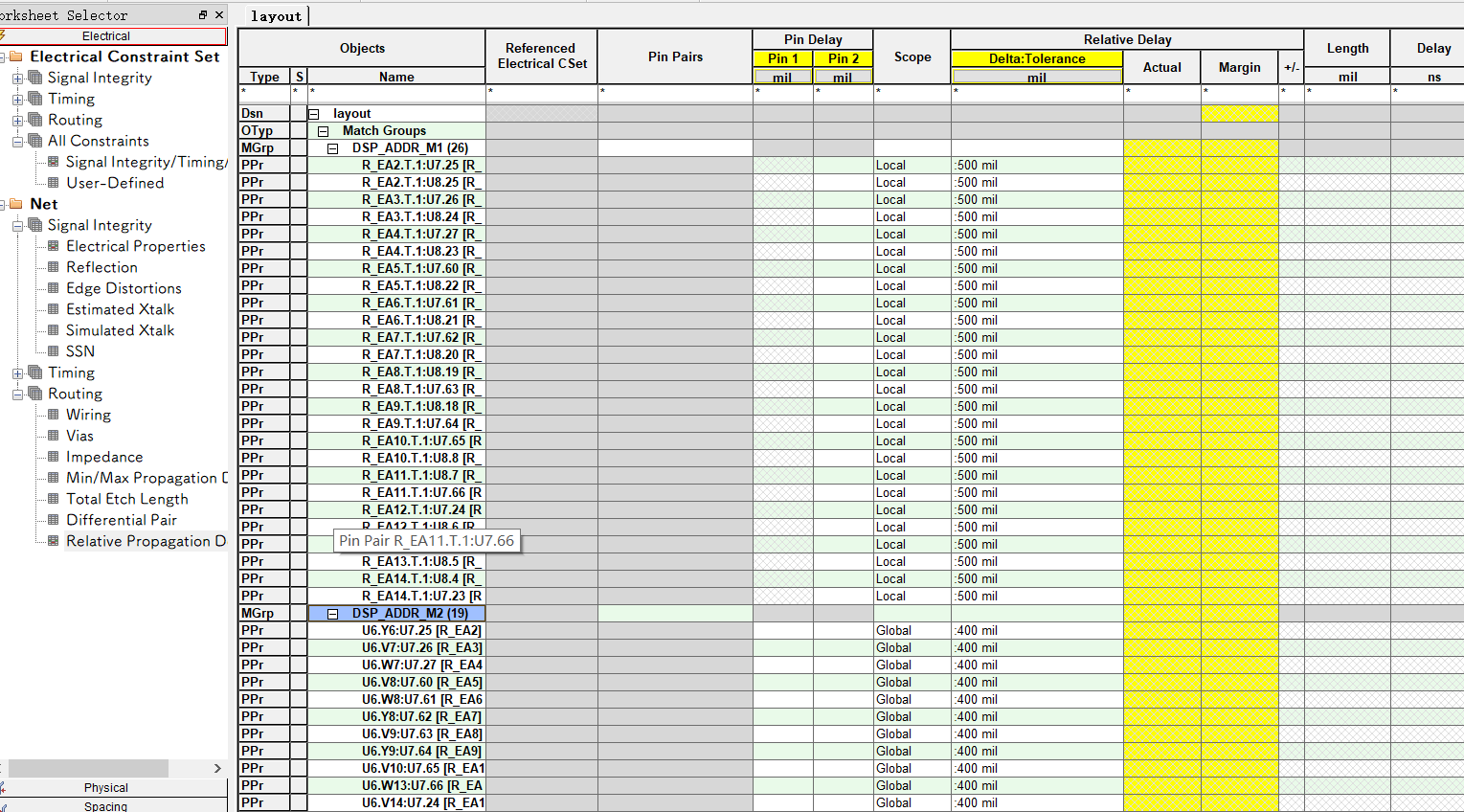

然后对DSP_ADDR进行相对延时约束,也就是常说的等长设置,设置对于控制时延很重要。调整信号建立时间和保持时间。此处有两种等长,一种是DSP到RAM的所有线要设置等长,另一种是T型连接点到flash和RAM之间的等长。

local是同一个分支之内选择,比如本例子的T型连接点之间。global是不同线段之间。先设置T型连接点到flash和RAM之间的等长。由于是同一个网络,所以名称Name取相同。

设置完成之后更新到cm约束管理器

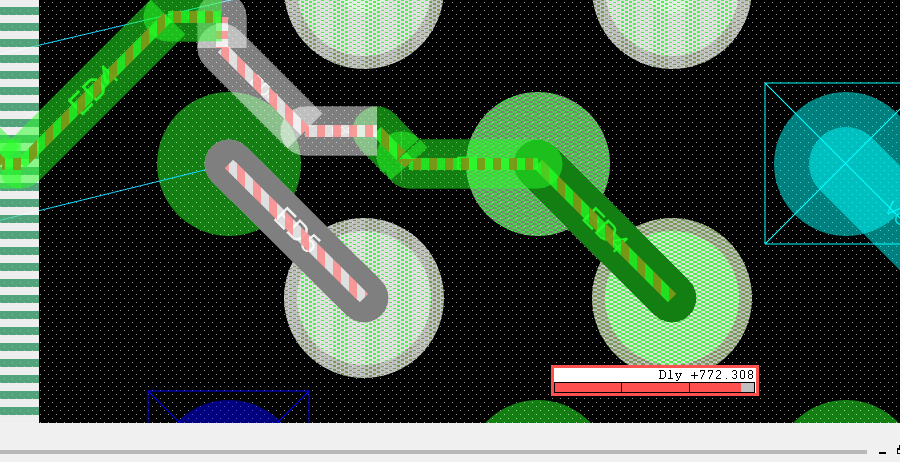

可以开始愉快的布线啦!

【转自:武汉网站建设公司 http://www.wh5w.com 复制请保留原URL】