博主福利:100G+电子设计学习资源包!

http://mp.weixin.qq.com/mp/homepage?__biz=MzU3OTczMzk5Mg==&hid=7&sn=ad5d5d0f15df84f4a92ebf72f88d4ee8&scene=18#wechat_redirect --------------------------------------------------------------------------------------------------------------------------

在一个复杂的设计中,我们往往会抓大量的信号,而ISE14.7编译代码的时候会把一些有相同逻辑的信号给优化掉,这会导致我们在选择信号的时候找不到想要抓取的信号,针对这种情况给大家提供两个解决办法。

方法一:

1、在你想要抓取的所有信号前面加上(*KEEP = “TRUE”*)

(*KEEP = "TRUE"*)reg [3:0] R_cnt;

Place the Verilog constraint immediately before the module or instantiation .

Specify the Verilog constraint as follows:

(* KEEP = “{TRUE|FALSE |SOFT}” *)

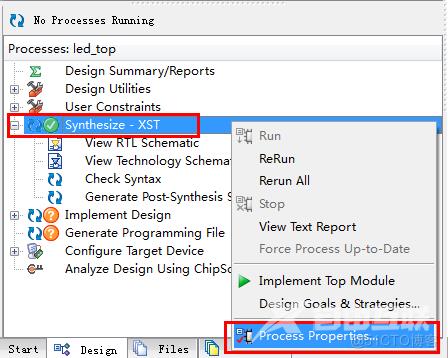

2、选中Synthesize-XST,鼠标右键在弹出的菜单栏中选择Process Properties...

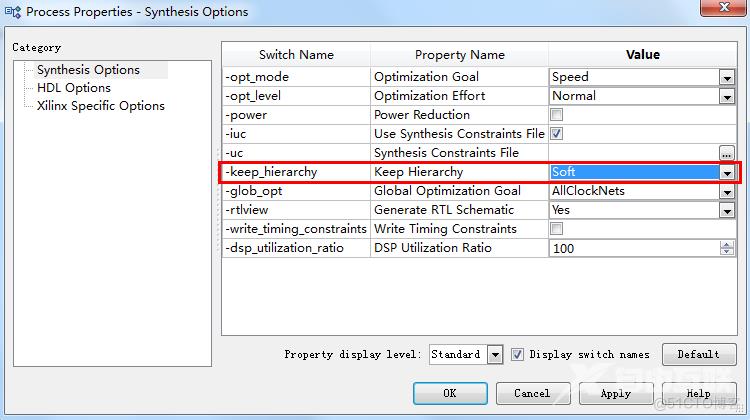

3、Synthesis_Options中的-keep hierarchy是设置综合后层次结构的。

如果选了这个,那么综合后MAP的时候就会保持你RTL设计的层次结构。

好处在于,设置之后,你用CHIPSCOPE调试时看到的层次结构跟你的设计是一样的,找信号很方便。

缺点在于,xilinx 的工具就不能在设计层次间进行设计优化了。

所以,建议你设成 “soft”,意思就是综合后保持层次结构,但是P&R的时候可以打破层次结构进行优化。

4、设置完毕以后重新综合,然后重新在.cdc选择要抓取的信号。

方法二:

上面一种方法根据我的经验并不能100%的保证信号不被综合掉,所以还有另外一种方法是写一段冗余逻辑把信号进行运算然后赋值给一个输出,并把输出引到顶层绑定一个空闲的管脚,这种情况我的处理方法是:

假设要抓取的信号是(*KEEP = "TRUE"*)reg [3:0] R_cnt;

1、定义1个输出信号O_test;

Output O_test;

2、把要抓取的信号各位相或然后赋值给O_test

assign O_test = | R_cnt ;

R_cnt前面的“|”表示把R_cnt的每一bit按位相或,这行代码和

assign O_test = R_cnt[0] | R_cnt[1] | R_cnt[2] ;

综合出来的逻辑是一模一样的

3、把O_test引到顶层并在约束文件中分配一个空余管脚

通过这种增加冗余逻辑的方式,R_cnt信号一般不会被综合掉,我自己在平时的使用中会先使用第一种方法,如果发现第一种方法还是把我想看的关键信号综合掉了的话就采用第二种方法。