Makefile

Makefile是一个文本文件,记录一个项目的构建规则流程。在工作中会不会写makefile,从一个侧面说明了一个人是否具备完成大型工程的能力,同时一个工程中的源文件不计数,其按类型、功能、模块分别放在若干个目录中,makefile定义了一系列的规则来指定,哪些文件需要先编译,哪些文件需要后编译,哪些文件需要重新编译,甚至于进行更复杂的功能操作,其带来的好处就是——“自动化编译”,一旦写好,只需要一个make命令,整个工程完全自动编

译,极大的提高了软件开发的效率。

make

make是一个命令工具,是一个解释makefile中指令的命令工具,一般来说,大多数的IDE都有这个命令,比如:Delphi的make,Visual C++的nmake,Linux下GNU的make。可见,makefile都成为了一

种在工程方面的编译方法。make是一条命令,makefile是一个文件,两个搭配使用,完成项目自动化构建。

工作原理

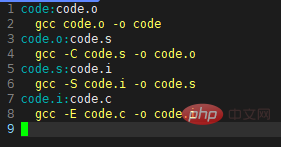

在Makefile中会形成各个文件之间的依赖关系,比如一个code.exe是在code.o 的基础上通过链接生成的,而code.o是在code.s的基础上通过汇编形成的,code.s是在code.i的基础上通过编译生成,code.i是在code.c的基础上预处理完成之后生成,如此层层寻找源头。其规则使用倒叙的方法,将第一个文件视作最后完后的文件,若当前文件未生成则通过依赖关系以及相互生成的方法进行层层推进,最终完成全部文件的形成。

依赖关系

A:B A是依赖于B

依赖方法

gcc 选项 + B -o +A A是B经过处理生成的文件

项目清理

工程是需要被清理的,像clean这种,没有被第一个目标文件直接或间接关联,那么它后面所定义的命令将不会被自动执行,不过,我们可以显示要make执行。即命令——“make clean”,以此来清除所有的目标文件,以便重编译。但是一般我们这种clean的目标文件,我们将它设置为伪目标,用 .PHONY 修饰,伪目标的特性是,总是被

执行的。

原理

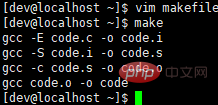

make会在当前目录下找名字叫“Makefile”或“makefile”的文件。

如果找到,它会找文件中内容中的第一个文件,并把这个文件作为最终的目标文件。

如果该文件当前不存在,或是该文件的依赖文件的修改时间要比当前这个文件要新,那么,他就会执行后面所定义的命令来生成当前文件。

如果该文件的依赖文件不存在,那么便对这个依赖文件进行如同第2,3步的步骤,知道找到最后的源文件为止

当然,你的C文件和H文件是存在的啦,于是make会生成 .o 文件,然后再用 .o 文件声明make的终极任务,也就是执行文件了。

这就是整个make的依赖性,make会一层又一层地去找文件的依赖关系,直到最终编译出第一个目标文件。

在找寻的过程中,如果出现错误,比如最后被依赖的文件找不到,那么make就会直接退出,并报错,而对于所定义的命令的错误,或是编译不成功,make根本不理。

make只管文件的依赖性,即,如果在我找了依赖关系之后,冒号后面的文件还是不在,那么对不起,我就不工作啦。

make 每次在Makefile中只会找到第一个目标对象进行生成,生成之后就会退出(不会生成第二个对象)

.PHONY: clean

clear:

rm -rf $(obj)

【补充】

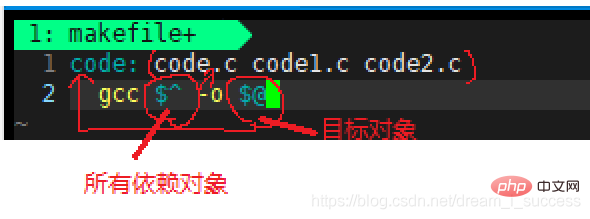

1.预定义变量的使用:[$@ ]、[ $^]、[ $<],可以用以上三个对文件名进行替换

$@ :表示目标对象

$^:表示所有依赖对象

&<:表示依赖对象的第一个

2. $ (wildcard ./.c)获取当前目录下所有的以.c结尾的文件的文件名称【例】 src=$(wildcard ./.c) code: $ (str)

3. $ (patsubst %.c, %.o,$(str))表示将str变量中的.c文件替换成.o,然后存放在obj变量中。

4. 伪对象:声明一个目标对象与外部文件无关,表示每次对这个对象不管是否最新都要重新生成,且不管外部是否能够存在,都要每次无论如何都执行语句[.PHONY:]

5.程序的编译过程:一般包含预处理、编译、汇编、链接,但是在实际项目构建中整体分为两步,即编译和链接。这样的好处在于,如果只是修改了一个.c文件,对于之前的直接对所有.c进行编译生成可执行程序的过程来说,需要重新编译所有的.c生成可执行程序,这样的效率非常低下,因此分为两步进行操作,先把每个.c都是生成自己的.o,然后再将所有的.o链接在一起,一旦一个.c发生改变只需要对这一个.c进行生成.o之后,替换程序中的指定模块就可以。

例1. 创建一个一般的Makefile

例2. 使用预定义编写的Makefile

相关推荐:《Linux视频教程》

以上就是带你掌握Linux项目自动化构建工具Makefile make的详细内容,更多请关注自由互联其它相关文章!