这几天一直在忙着面试,在面的过程中发现自己之前的学习只是局限于verilog,SV的语法还有UVM验证方法学等验证工具上面,缺乏对整个芯片设计流程的视角和大局观。 初学者对前仿、后

这几天一直在忙着面试,在面的过程中发现自己之前的学习只是局限于verilog,SV的语法还有UVM验证方法学等验证工具上面,缺乏对整个芯片设计流程的视角和大局观。

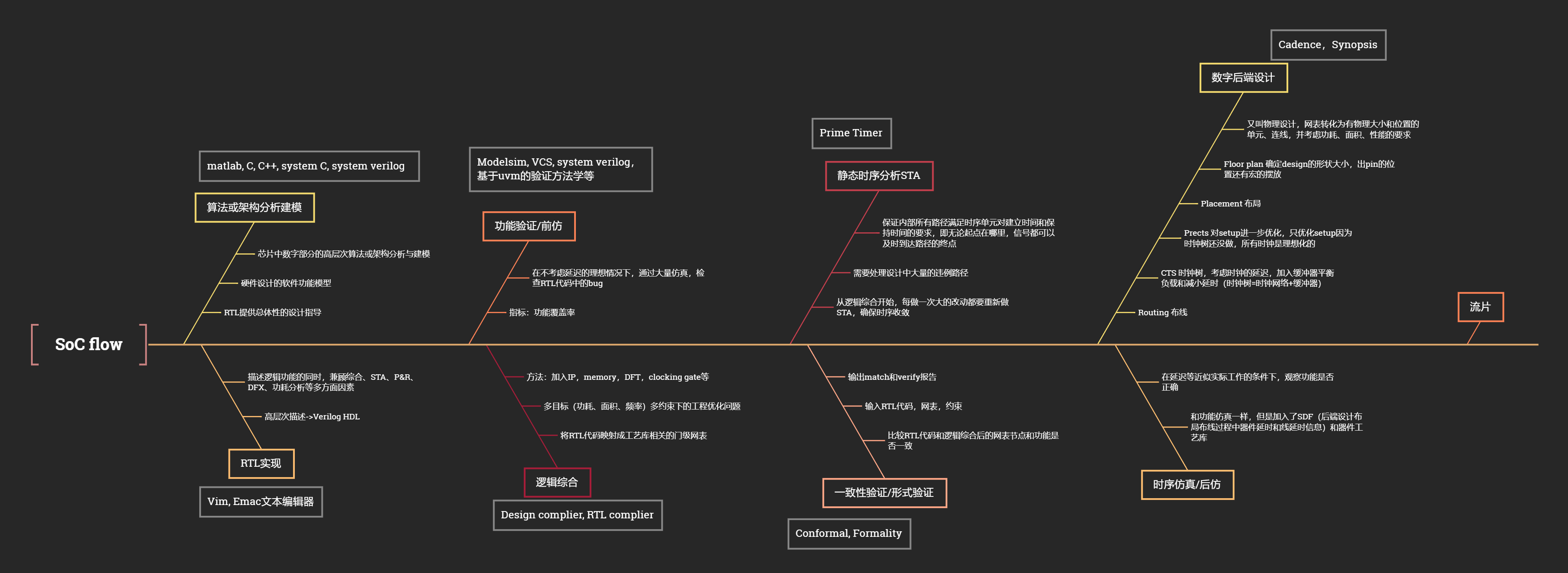

初学者对前仿、后仿、功能验证、形式验证、综合、时序分析这些名词感觉比较陌生,因此我整理了一下SoC的设计流程,分别是根据时间线(从提出idea到交给工厂流片)和芯片的描述层次(从高层次描述到电路版图)来总结的,分享给大家。

首先是SoC flow的一个呈现,灰色方框中是用到的语言或EDA工具

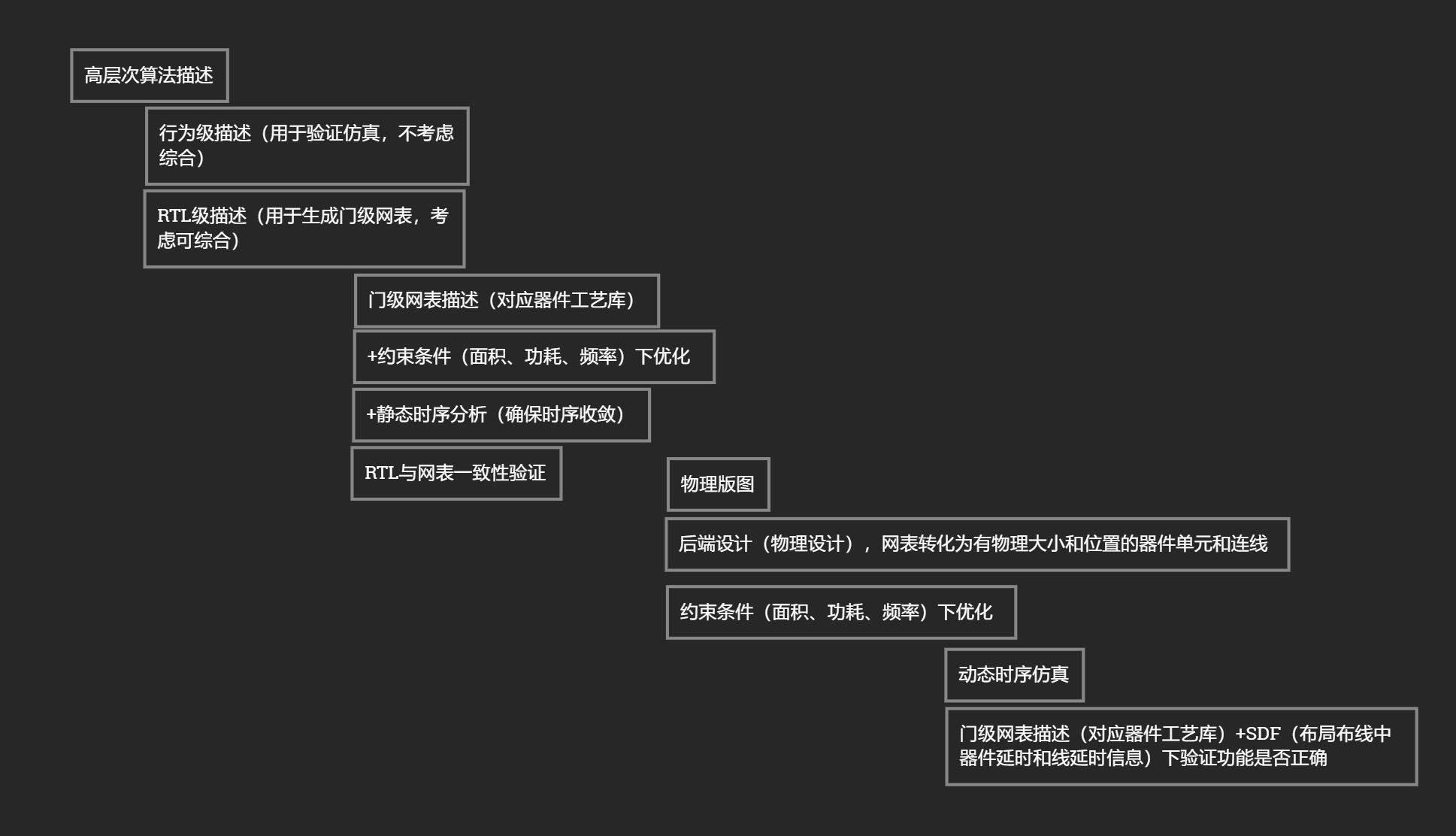

简易版本:

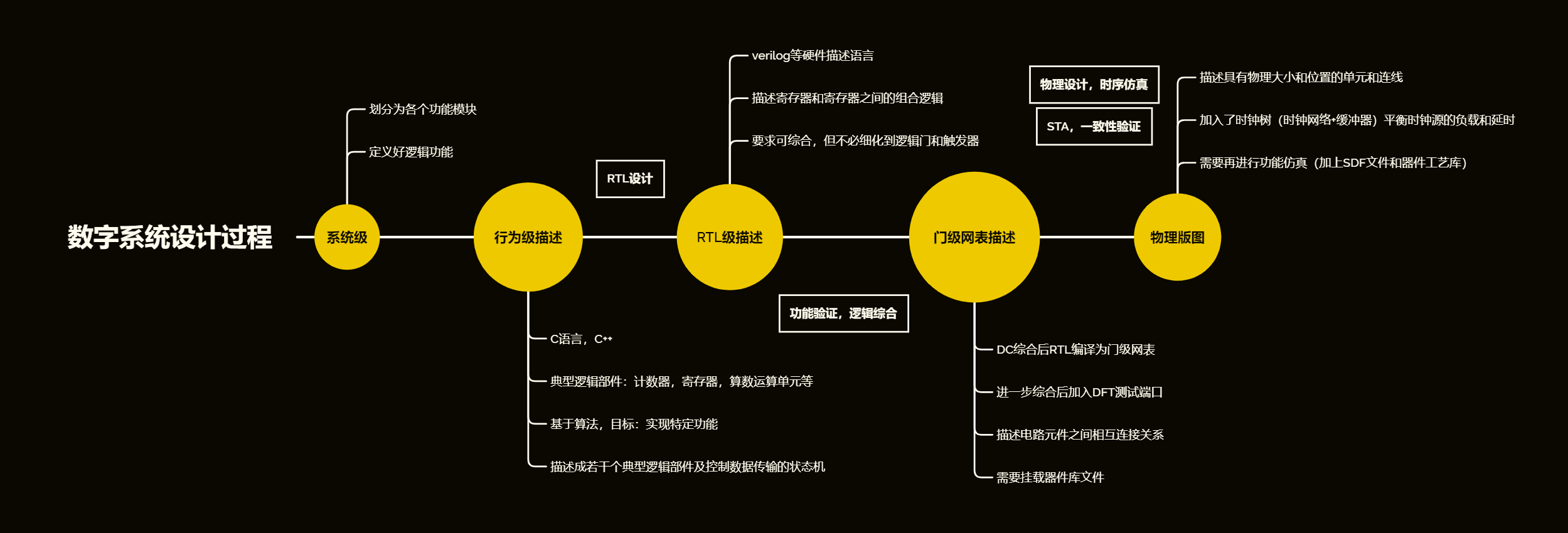

然后是数字电路设计流程: