开发环境:vivado 2018.2、PetaLinux 2018.2

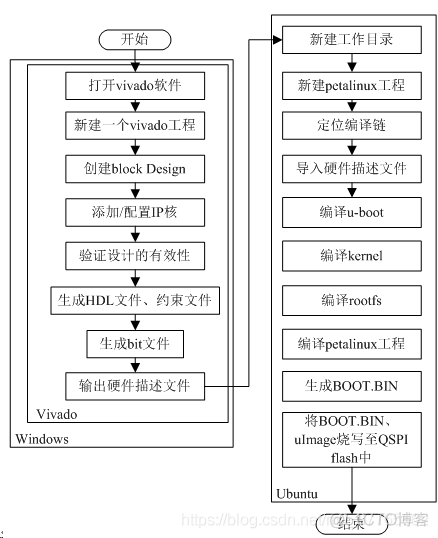

程序框架:

具体步骤:

1. 打开vivado 2018.2软件

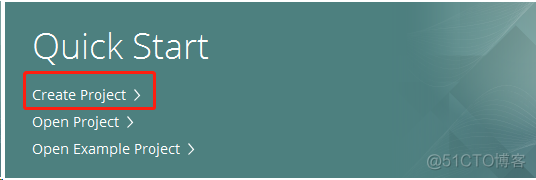

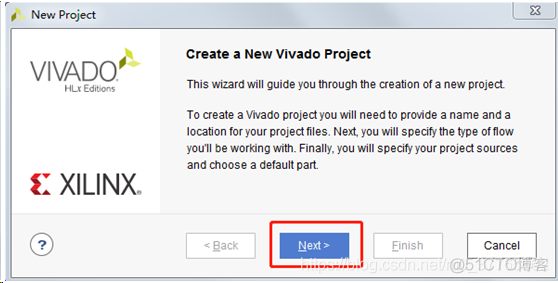

2. 点击Create Project

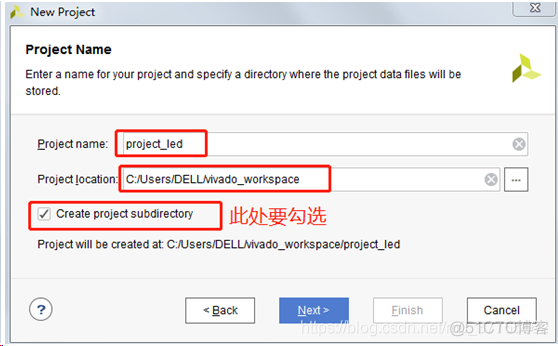

3. 输入工程名和工程路径

(注意:工程路径中不要有空格,否则后续SDK会无法导入硬件描述文件)

4. 选择RTL工程,下方选项不勾选。

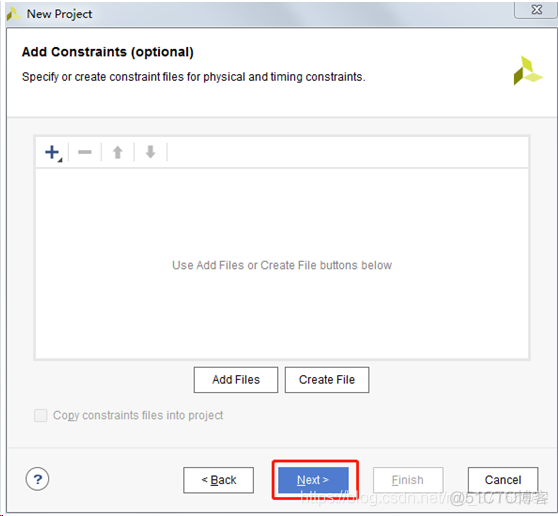

5. 选择Verilog语言,不添加文件,一直点击Next

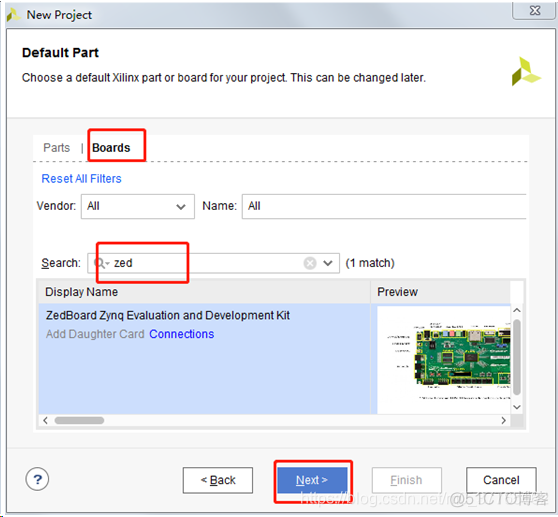

6. 直接点击boards,选择对应的开发板

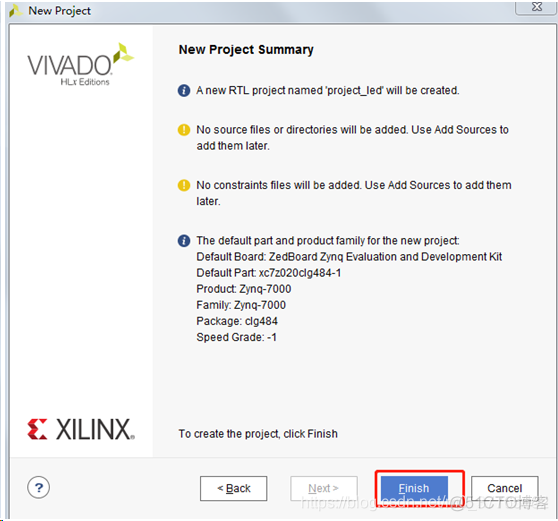

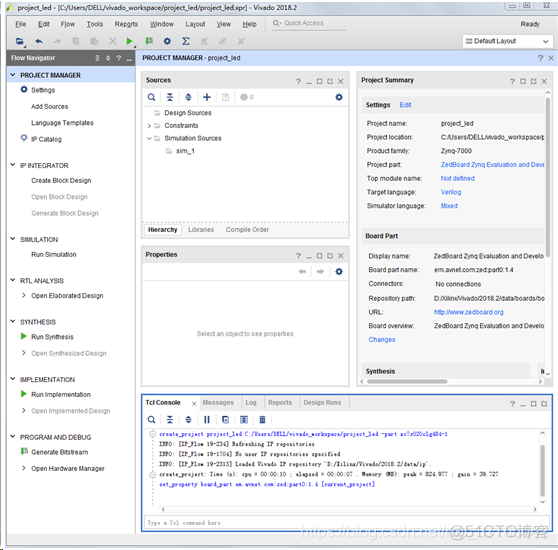

7. 打开一个新项目project_led

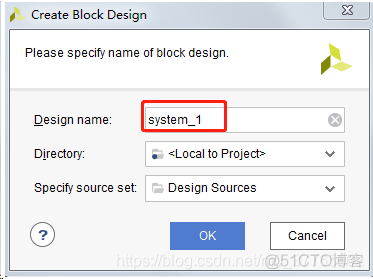

8. 创建一个block Design ,在Flow Navigator区域展开IP INTEGRATOR,选择create Block Design,输入块的名称system_1。

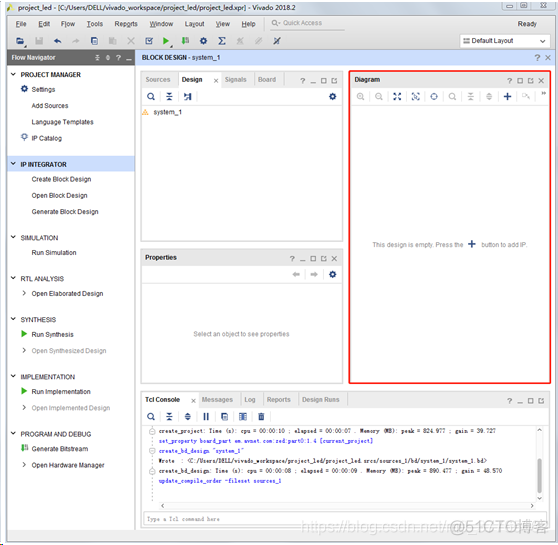

9. 工作域将会打开Diagram的图表画布,我们将在空白区域像画画一样构建自己的系统。这里操作的最小单位为IP核,xilinx提供的免费IP核可以直接添加使用,用户也可以自定义IP核。

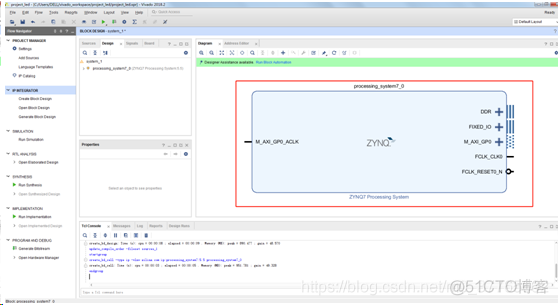

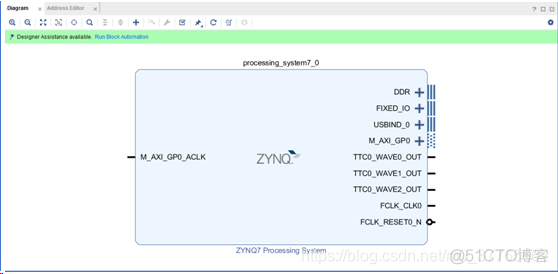

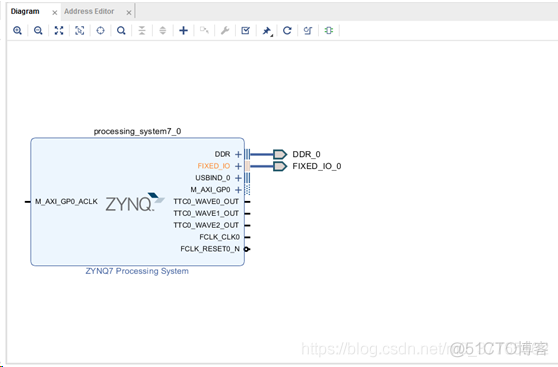

10. 点击空白画布中间的+号来添加IP核(或者在空白板上右键点击Add IP),在search中输入zynq ,在搜索结果中双击ZYNQ7 Processing? system添加PS端到IP核画布

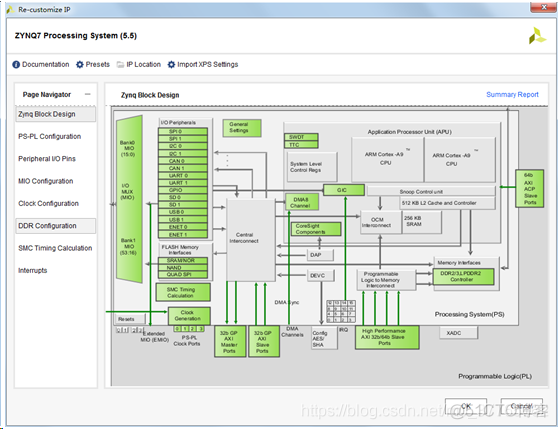

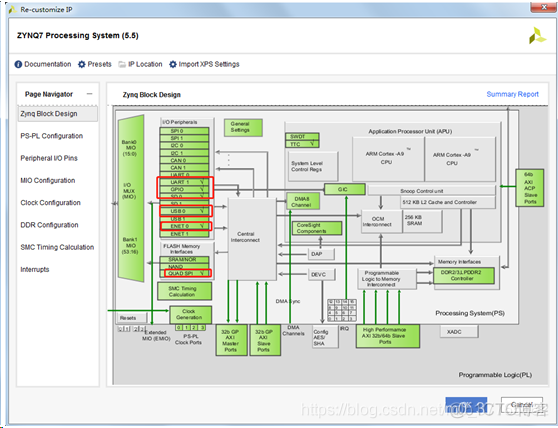

11. 要使PS模块在zedboard中工作,还要对其进行配置,鼠标左键双击PS模块,即可打开编辑IP核的界面。

12. 点击Presets -> Zedboard ,使用vivado对zedboard提供的默认配置,点击ok。(此处用户可根据自己的硬件自行配置)

13. 单击DDR接口,出现笔状时右键,选择 Make External ,FIXED_IO使用同样办法

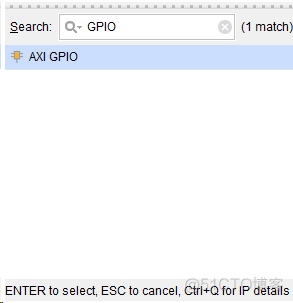

14. 添加AXI GPIO IP核到系统中。右键单击空白处添加IP核,搜索栏输入GPIO,双击AXI GPIO 添加完成

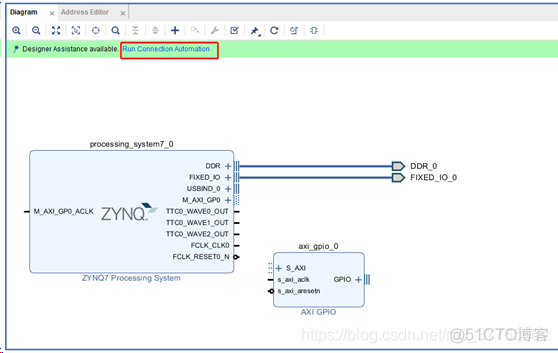

15. 然后单击run connection automation 选择/axi_gpio_o/s_AXI,单击ok有两个新IP核被自动添加了。

16. 然后再单击run connection automation,Select Board Interface下选择leds_8bits.

这样就基本配置完成,IP Integrator会自动为AXI总线上的逻辑设备分配地址空间,这样ARM就可以寻址到该设备。如图:

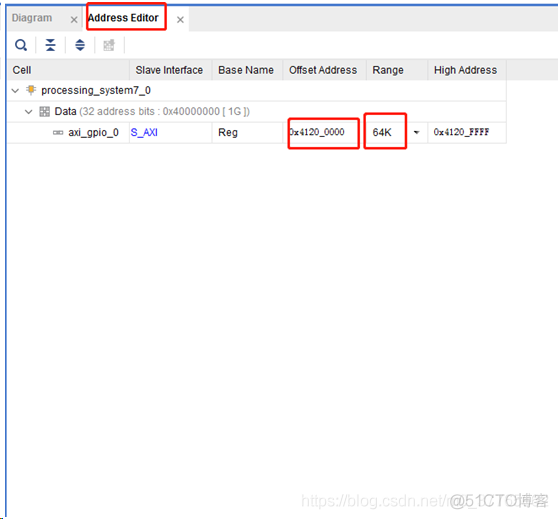

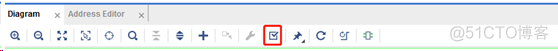

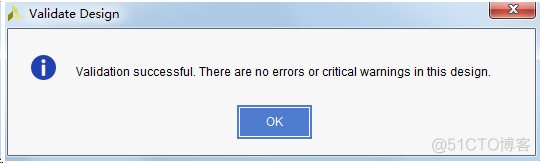

17. 为AXI GPIO分配64k的地址空间,基地址为0x41200000,保存工程。在Diagram窗口上方工具栏中,选择Validate Design 按钮,检查设计有效性

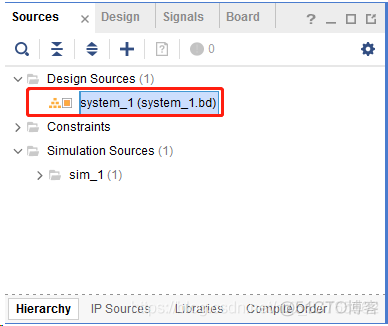

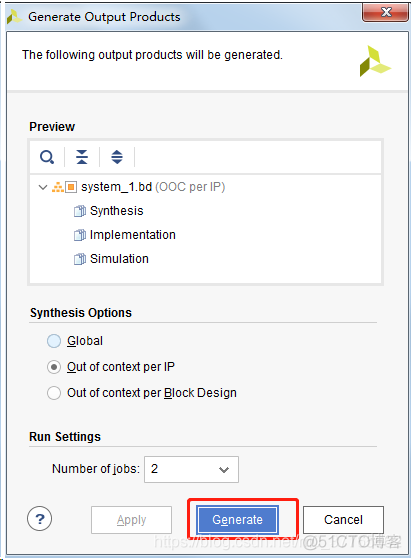

18. 至此,IP子系统我们已经设计完成了。下面我们将设计完成Block Design生成可以综合的HDL设计文件。 在Sources 窗口,右键zynq_system_1 选择Generate Output Products

19. 单击Generate,生成HDL源文件和相应端口的约束文件。再右击zynq_system_1,选择Create HDL Wrapper选型,单击ok。这里vivado为IP子系统生成了一个顶层文件,使我们可以对系统进行综合、实现并生成比特流。

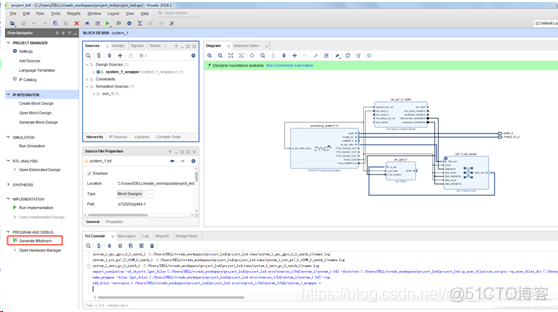

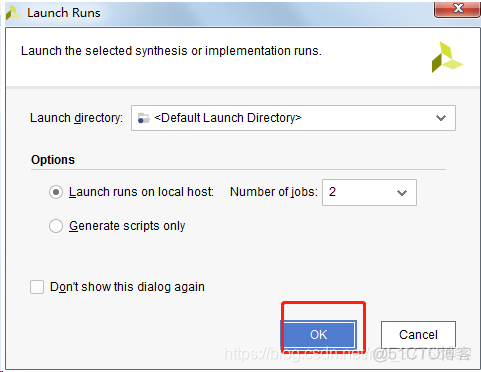

20. 在Flow Navigator 中展开Program and debug ,单击generate Bitstream。单击ok。此时vivado会生成一个硬件.bit文件,产生的bit文件位于:C:\Users\DELL\vivado_workspace\project_led\project_led.runs\impl_1中

?

21. 这一过程将持续很长时间,当完成后,会弹出一个对话框,选择open Implementation Design

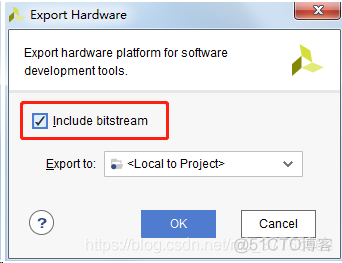

22. 将设计导入SDK,然后就可以对ARM编程。选中Sources栏中的zynq_system_1.bd,执行File->Export->Export Hardware 命令,弹出的对话框确保复选按钮被选上。会生成一个project_led.sdk文件夹 (产生的硬件描述文件system_1_wrapper.hdf文件位于C:\Users\DELL\vivado_workspace\project_led\project_led.sdk)

?

23. 打开VMware虚拟机,运行Ubuntu 16.04.3操作系统。

24. 定位目录:先在shell中找一个准备存放工程的地方,(我的是/home/admin-hjj/program),命令行

cd /home/admin-hjj/program/

25. 定位编译链,启动PetaLinux:根据安装petalinux的路径:

source /home/admin-hjj/PetaLinux/settings.sh

26. 创建PetaLinux工程:将在PRO目录下面,创建一个工程:

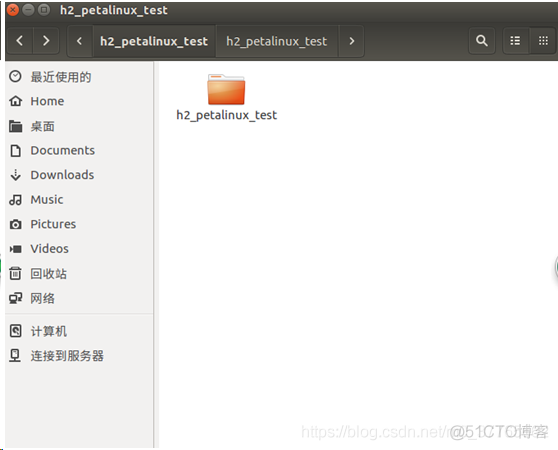

petalinux-create --type project --template zynq --name h2_petalinux_test

° zynqMP (for UltraScale+ MPSoC)

° zynq (for Zynq)

° microblaze (for MicroBlaze)

h2_petalinux_test是工程名,该命令会自动在program文件夹里创建h2_petalinux_test文件夹。

27. 引用刚才输出的硬件描述文件:把之前导出的硬件描述文件design_ZYNQ_wrapper.hdf拷贝到虚拟机中的h2_petalinux_test工程文件夹下,然后在shell中输入:

cd h2_petalinux_test //进入到petalinux工程目录下

petalinux-config --get-hw-description=/home/admin-hjj/program/h2_petalinux_test

注意:此命令中不可随意添加空格,要先进入petalinux工程目录下再执行此命令。

会进入一个配置界面,在里面我们可以配置一些系统参数,主要的配置包括:启动方式,启动存储器分区表,启动文件名称等等,本文暂不对其修改(默认是从SD卡中启动),然后等待其配置(时间较长)

*** End of the configuration.

*** Execute 'make' to start the build or try 'make help'.

[INFO] sourcing bitbake

[INFO] generating plnxtool conf

[INFO] generating meta-plnx-generated layer

[INFO] generating machine configuration

[INFO] generating bbappends for project . This may take time !

[INFO] generating u-boot configuration files

[INFO] generating kernel configuration files

[INFO] generating kconfig for Rootfs

[INFO] oldconfig rootfs

[INFO] generating petalinux-user-image.bb

28. 获取文件夹权限 :在上一步完成后,输入命令sudo chmod -R 777 /home/hlf获取文件夹权限(工程文件夹和petalinux的安装文件夹),否则编译的时候,会发生错误。

sudo chmod -R 777 /home/admin-hjj/program/h2_petalinux_test

目前为止,在shell中的命令既可以以超级用户su的身份运行也可以以普通用户的方式运行(建议全部都用普通用户的方式,免得切换),但是等下编译u-boot和kernel以及rootfs的时候,必须以普通用户的身份运行命令行,否则会报错的。

29. 编译u-boot

注意:到此处的时候,不能再用超级用户了,要切换到普通用户下,之后的所有操作都在普通用户下

普通用户的shell中输入

petalinux-config -c u-boot

(依然要事先输入source /home/hlf/mnt/petalinux/settings.sh命令),然后等待GUI出来,这里暂时不改动啥,直接save(save为u-boot.config,名字随便取但不要留空),然后继续等(新建工程要等的时间还是比较长的,后来就会好的。

30. 编译kernel

petalinux-config -c kernel

31. 编译文件系统

petalinux-config -c rootfs

32. 编译工程

petalinux-build

会自动在images/linux生成zynq_fsbl.elf文件。

33. 生成BOOT.BIN

把shell定位到image/linux目录下,同时将vivado中生成的.bit文件拷贝至image/linux,执行命令:

petalinux-package --boot --format BIN --fsbl zynq_fsbl.elf --fpga system_wrapper.bit --u-boot

在文件夹下就可以发现,多了一个BOOT.BIN