DDR3 和 DDR4 的豁口不一样,主板所支持的 DDR 类型不同。

DDR SRAM(Double Data Rate Synchronous Dynamic Random Access Memory):双倍数据率同步动态随机存取存储器,

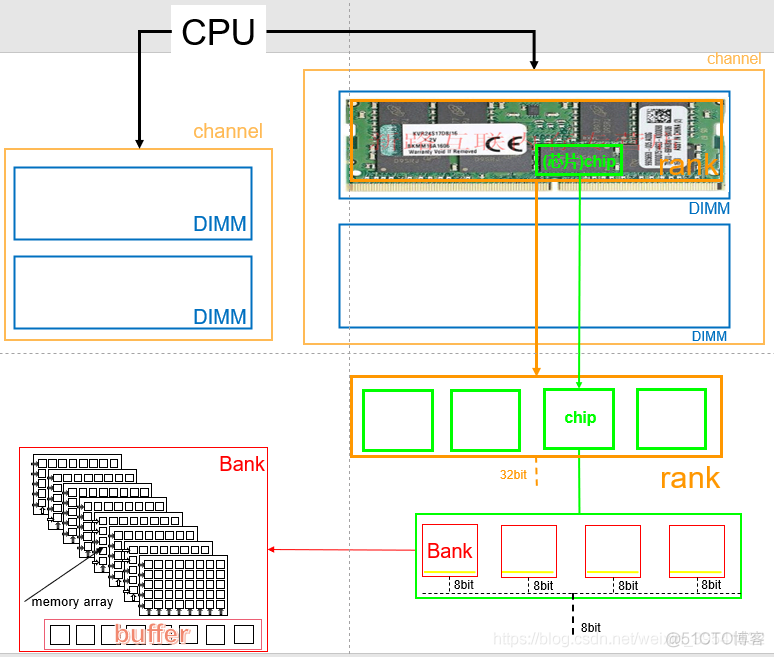

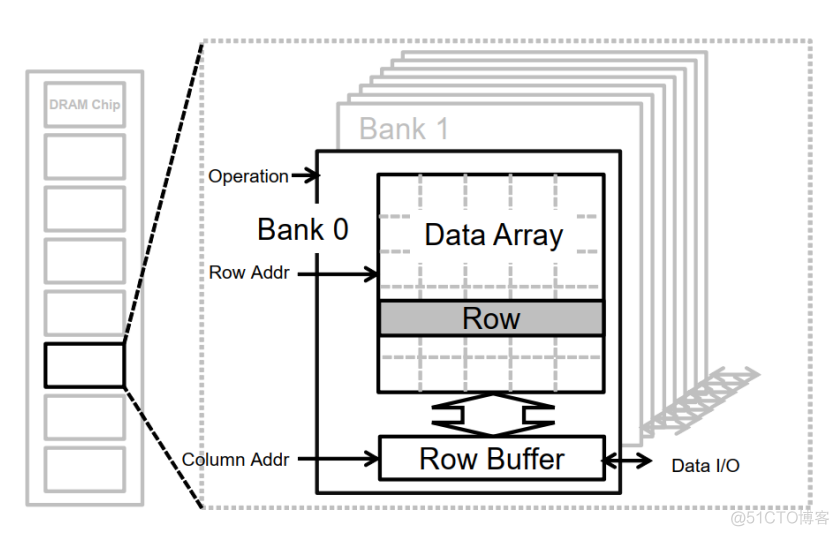

Channel、DIMM、Rank、Chip、Bank、Row/Column

勘误:非 32bit,8bit。rowbuffer可能多达4KB(有论文指出,rowbuffer是一页大小),多次内存请求均可命中同一rowbuffer。一个chip中包含多个bank,但是一个bank只有一个矩阵。

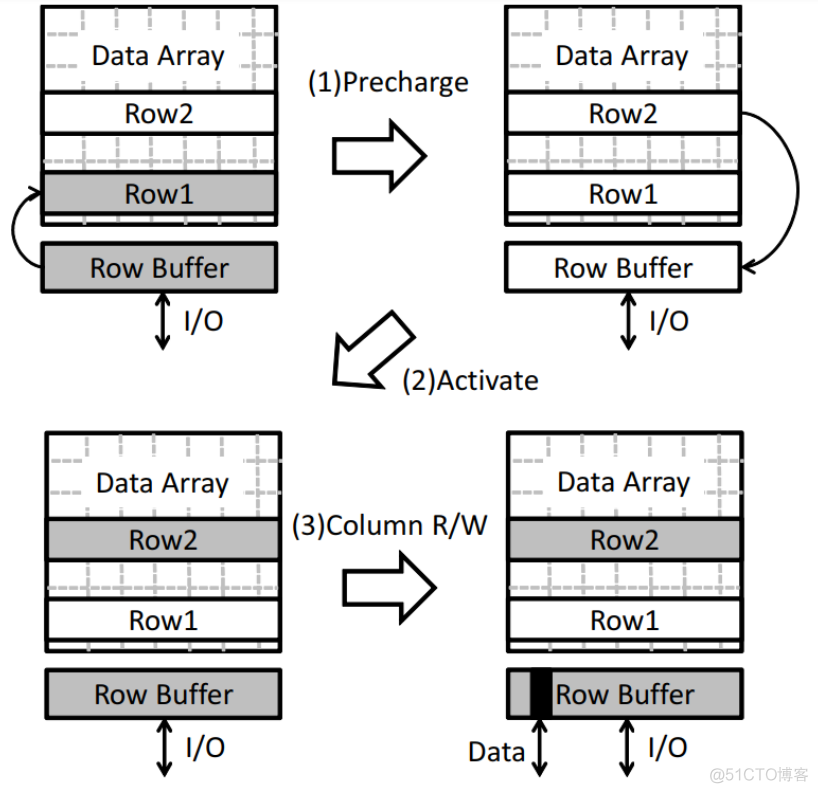

访存过程

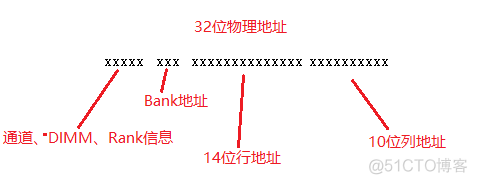

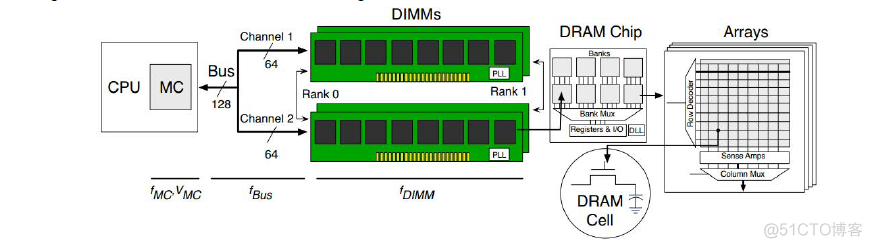

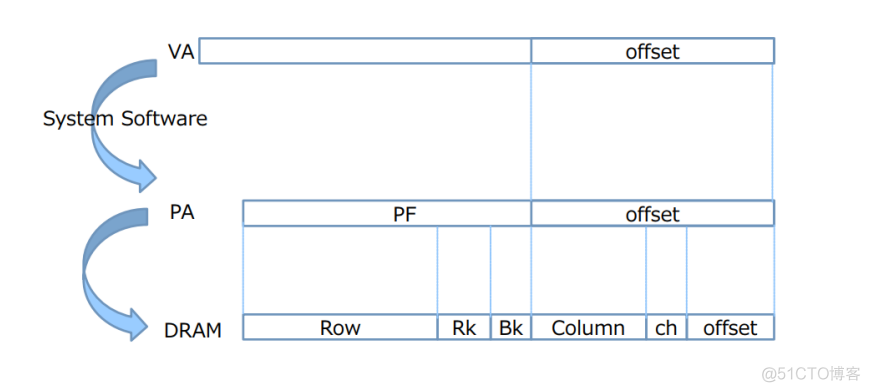

物理地址 - MMU --> CPU – DMI 总线 --> 北桥(内存控制器) – 解析数据(地址)–> Channel、DIMM、Rank(Side)、Chip、Bank、Row/Column …

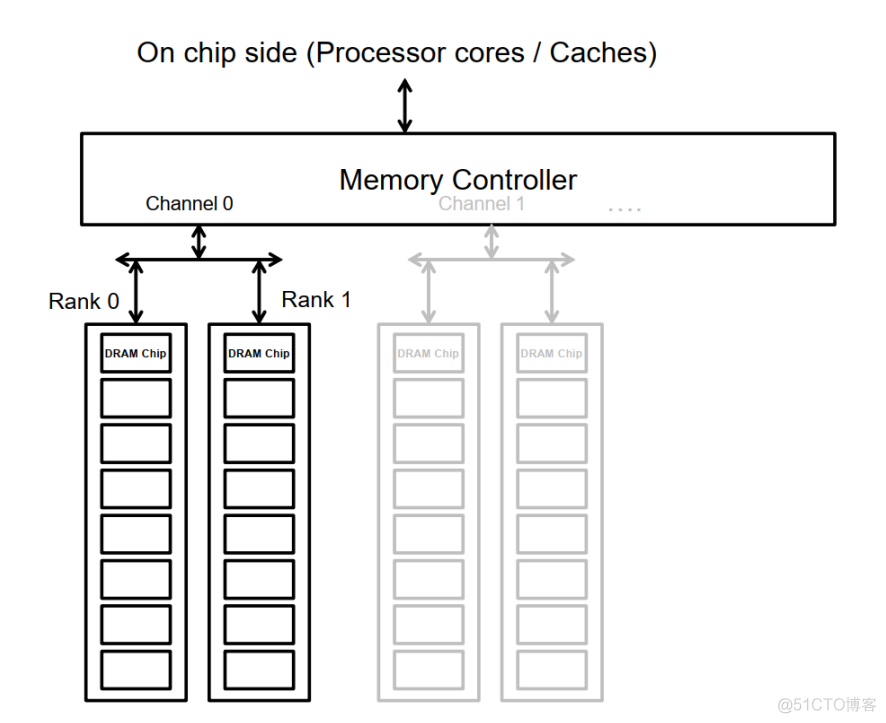

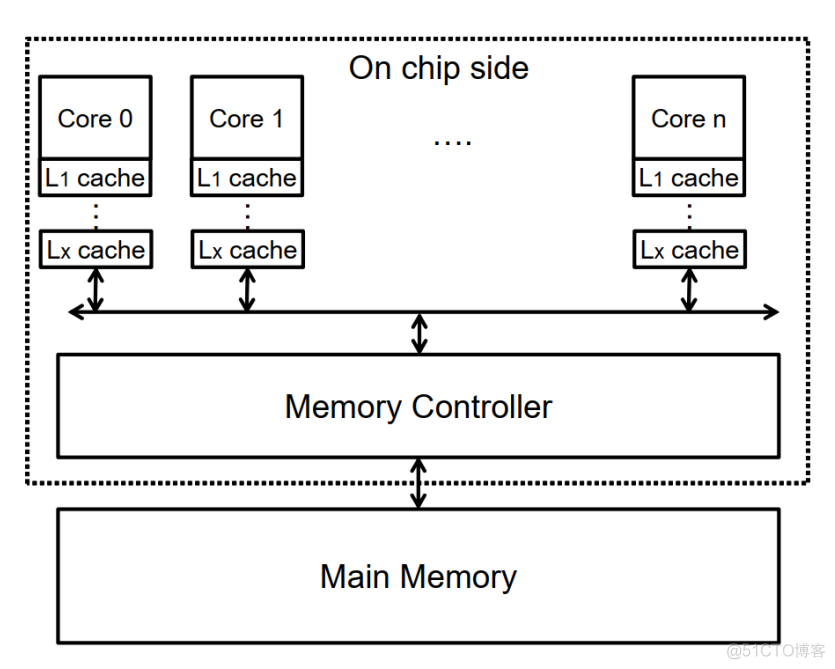

Channel

意味着在北桥(CPU外核)存在 Channel 个内存控制器,每个内存控制器控制一个内存通道,理论上内存带宽增加一倍。

DIMM

Dual in-line memory module

双面 RANK 条,与 SIMM 区别。

Rank(Side物理 bank)

CPU 与内存之间的接口位宽是 64 位,意味着 CPU 在一个周期内会与内存交互 64 bit 的数据,但是 单个内存颗粒(Chip) 的位宽不足 64 bit,大多只有 4bit、8bit 和 16bit,需要将多个内存颗粒并联起来,组成一个位宽为 64bit的数据集合,该集合称为 Physical Bank(RANK)。

RANK 其实是一组内存颗粒位宽的集合,也可以叫 Chips,在 PCB上,往往把一面上的内存颗粒组成一个 RANK,另一面为另一个 RANK,这样的 RANK 也可称为 Side。

RANK 由多个 chips 连接到同一个片选信号组成,北桥(内存控制器)能够对同一个 RANK 的所有 chips 同时进行读写操作(一次性能够处理 64 位数据)。

要准确知道内存条实际物理BANK数量,我们只要将单个芯片的逻辑BANK数量和位宽以及内存条上芯片个数搞清楚。各个芯片位宽之和为64就是单物理BANK,如果是128就是双物理BANK。

Chip

存储芯片(内存颗粒),提供存储功能,Chip 里面包含多个 Bank。

一个 RANK 由多个 chips 组成 64bit,即由多个 chips 中的 bank 并联成 64bit 数据??。

芯片逻辑BANK位宽目前的工艺水平只能最多做到16位,因此大家看到几乎所有的芯片逻辑BANK位宽只可能4/8/16三者之一。

Bank(逻辑 bank)

Bank 由很多的 Cell 组成,由行列确定一个 Cell。

具有两个逻辑 bank 的 32Mbit 芯片:K4S160822DT(1M(cell 个数) x 8Bit(cell 大小、芯片位宽) x 2 BANK)

物理 bank (RANK)与逻辑 bank:

对于64Mbit 逻辑 bank (4M*16) 来说,逻辑 bank 带宽 16bit,8颗逻辑 bank 带宽=16*8=128bit(即两个RANK),4 颗逻辑 bank 带宽=16*4=64bit(即一个RANK)。两个物理BANK(两个 RANK)的情况只有出现在位宽超出了 64 位的情况下(即位宽出现了富余),由于芯片组(逻辑 bank组,RANK)任一时刻只能处理一个64位,所以才分成两个物理BANK(两个 RANK)。

Row/Column

物理地址中的 cell 位数,单位应该是 bit,2**3:表示一个 cell 大小为 8bit。